- 1.18 MB

- 2022-04-29 14:39:38 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

'基本数字逻辑单元的设计

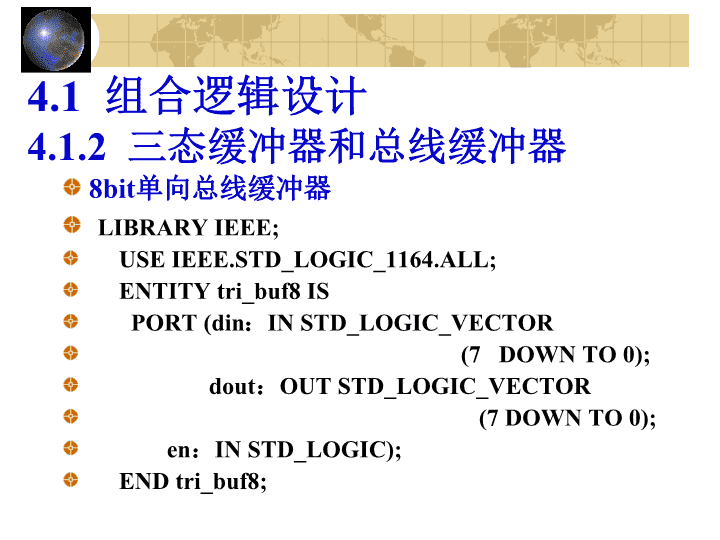

4.1组合逻辑设计4.1.2三态缓冲器和总线缓冲器8bit单向总线缓冲器LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYtri_buf8ISPORT(din:INSTD_LOGIC_VECTOR(7DOWNTO0);dout:OUTSTD_LOGIC_VECTOR(7DOWNTO0);en:INSTD_LOGIC);ENDtri_buf8;

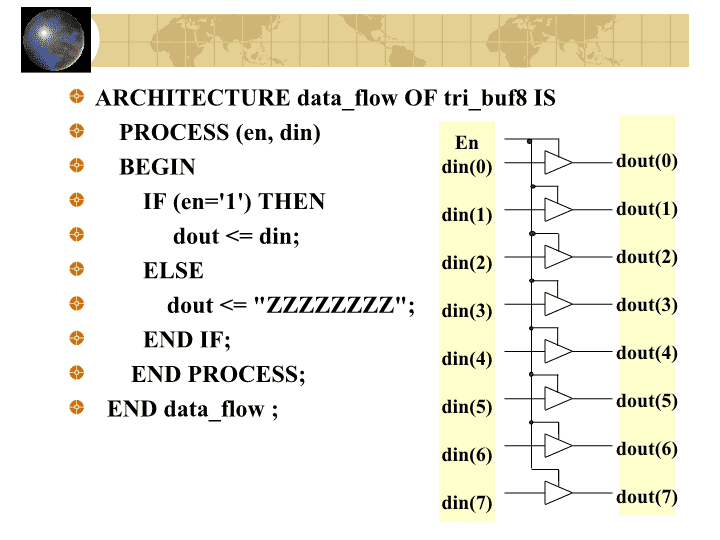

ARCHITECTUREdata_flowOFtri_buf8ISPROCESS(en,din)BEGINIF(en="1")THENdout<=din;ELSEdout<="ZZZZZZZZ";ENDIF;ENDPROCESS;ENDdata_flow;Endin(0)din(1)din(2)din(3)din(4)din(5)din(6)din(7)dout(0)dout(1)dout(2)dout(3)dout(4)dout(5)dout(6)dout(7)

BCD码—段选码译码器。BCD码输入与LED显示器字段的对应关系BCD码数字显示段hgfedcba0000011000000000111111100100102101001000011310110000010041001100101015100100100110610000010011171010011110008100000001001910010000其它11111111BCD-段选码译码器d0d1d2d3abc.hgdefVcc

LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYseg_delISPORT(d:INSTD_LOGICVECTOR(3DOWNTO0);q:OUTBIT_VECTOR(7DOWNTO0));ENDseg_del;ARCHITECTUREseg_rtlOFseg_delISBEGINPROCESS(d)BEGINCASEdISWHEN"0000"=>q<="11000000";WHEN"0001"=>q<="11111001";

WHEN"0010"=>q<="10100100";WHEN"0011"=>q<="10110000";WHEN"0100"=>q<="10011001";WHEN"0101"=>q<="10010010";WHEN"0110"=>q<="10000010";WHEN"0111"=>q<="11011000";WHEN"1000"=>q<="10000000";WHEN"1001"=>q<="10010000";WHENOTHERS=>q<="11111111";ENDCASE;ENDPROCESS;ENDseg-rtl;

4.1.4运算器的设计一位全加器的设计.LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYfull_adderISPORT(a,b,ci:INSTD_LOGIC;sum,cout:OUTSTD_LOGIC);ENDfull_adder;ARCHITECTURErtlOFfull_adderISBEGINsum<=aXORbXORci;cout<=(aANDb)OR(aANDci)OR(bANDci);ENDrtl;asumbcicout

4位串行进位加法器ciabsumcociabsumcociabsumcociabsumcoS0S1S2S3COCIA0B0A1B1A2B2A3B3SUMCIABSUMCIABSUMCIABSUMCIABCI0A0B0CI1A1B1CI2A2B2CIn-1An-1Bn-1进位产生逻辑S0S1S3Sn-1coutCIA[0:n-1]B[0:n-1]N位超前进位加法器

超前进位加法器各位加法器产生进位的逻辑表达式为:定义为进位生成函数,定义为进位传递函数,则全加器的各位和为:

4位超前进位加法器LIBRARYIEEE;USEIEEESTD_LOGIC_1164.ALL;ENTITYadder4ISPORT(a,b:INSTD_LOGIC_VECTOR(3DOWNTO0)ci:INSTD_LOGIC;sum:OUTSTD_LOGIC_VECTOR(3DOWNTO0);cout:OUTSTD_LOGIC);ENDadde4r;ARCHITECTURErtl_adder4OFadder4ISSIGNALg,p,c:STD_LOGIC_VECTOR(3DOWNTO0);BEGINp(0)<=a(0)ORb(0);p(1)<=a(1)ORb(1);p(2)<=a(2)ORb(2);g(0)<=a(0)ANDb(0);a[3:0]b[3:0]ciSum[3:0]cout

g(1)<=a(1)ANDb(1);g(2)<=a(2)ANDb(2);g(3)<=a(3)ANDb(3);c(0)<=g(0)OR(p(0)ANDci);c(1)<=g(1)OR(p(1)ANDg(0))OR(p(1)ANDp(0)ANDci);c(2)<=g(2)OR(p(2)ANDg(1))OR(p(2)ANDp(1)ANDg(0))OR(p(2)ANDp(1)ANDp(0)ANDci);c(3)<=g(3)OR(p(3)ANDg(2))OR(p(3)ANDp(2)ANDg(1))OR(p(3)ANDp(2)ANDp(1)ANDg(0))OR(p(3)ANDp(2)ANDp(1)ANDp(0)ANDci);cout=c(3);sum(0)<=a(0)XORb(0)XORci;sum(1)<=a(1)XORb(1)XORc(0);sum(2)<=a(2)XORb(2)XORc(1);sum(3)<=a(3)XORb(3)XORc(2);ENDrtl_adder4;

2.移位器8bit移位器。D7D6D5D4D3D2D1D0d7d6d5d4d3d2d1d0右移d0左移d7d6d5d4d3d2d1d0d7d6d5d4d3d2d1d0d7Irsrsldataa_outdata_inil

8bit移位器的VHDL程序。LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYshifterISPROT(data_in:INSTD_LOGIC_VECTOR(7DOWNTO0);sr,sl,ir,il:INSTD_LOGIC;data_out:OUTSTD_LOGIC_VECTOR(7DOWNTO0);ENDshifter;ARCHITECTUREAlgOFshifterISBEGINPROCESS(sr,sl,data_in,ir,il)VARIABLEcon:STD_LOGIC_VECTOR(0TO1);

BEGINcon:=sr&sl;CASEconISWHEN"00"=>data_out<=data_in;WHEN"01"=>data_out<=data_in(6DOWNTO0)&il;--左移WHEN“10”=>data_out<=ir&data_in(7DOWNTO1);--右移WHEN"11"=>data_out<=data_in;ENDCASE;ENDPROCESS;ENDAlg;

3.求补器LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;USEIEEE.STD_LOGIC_ARITH.ALL;USEIEEE.STD_LOGIC_UNSIGNED.ALL;ENTITYcomplementISPORT(a:INSTD_LOGIC_VECTOR(7DOWNTO0);b:UTSTD_LOGIC_VECTOR(7DOWNTO0));ENDcomplement;ARCHITECTURErtlOFcomplementISBEGINb<=NOTa+”00000001”;ENDrtl;

4.乘法器。部分积右移8bit乘法器的设计。LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;USEIEEE.STD_LOGIC_ARITH.ALL;USEIEEE.STD_LOGIC_UNSIGNED.ALL;ENTITYmultISPORT(ai,bi:INSTD_LOGIC_VECTOR(7DOWNTO0);Product:OUTSTD_LOGIC_VECTOR(15DOWNTO0);done:OUTSTD_LOGIC);ENDmult;

ARCHITECTUREshift_multOFmultISBEGINPROCESS(ai,bi)VARIABLEa,b,m:STD_LOGIC_VECTOR(8DOWNTO0);VARIABLEcount:INTEGER;BEGINa:="0"&ai;b:="0"&bi;count:=0;m:="00000000";done<="0";

WHILEcount<8LOOPIFa(0)="1"THENm:=m+bi;ENDIF;a:=m(0)&a(7DOWNTO1);m:="0"&m(7DOWNTO1);count:=count+1;ENDLOOP;product<=m(7DOWNTO0)&a(8DOWNTO1);done<="1";ENDPROCESS;ENDshift_mult;

4.1.5算术逻辑运算单元本例是一个8bit的ALU,能够完成8种运算,即加(add),带进位加(addc),减sub,带借位减法(subc),逻辑非、与、或和逻辑异或。alucoder程序包定义指令码。LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;PACKAGEalucoderISCONSTANTadd:STD_LOGIC_VECTOR(2DOWNTO0):="000";CONSTANTaddc:STD_LOGIC_VECTOR(2DOWNTO0):="001";CONSTANTsub:STD_LOGIC_VECTOR(2DOWNTO0):="010";

CONSTANTsubc:STD_LOGIC_VECTOR(2DOWNTO0):="011";CONSTANTnot:STD_LOGIC_VECTOR(2DOWNTO0):="100";CONSTANTand:STD_LOGIC_VECTOR(2DOWNTO0):="101";CONSTANTor:STD_LOGIC_VECTOR(2DOWNTO0):="110";CONSTANTxor:STD_LOGIC_VECTOR(2DOWNTO0):="111"ENDalucoder;

ALU运算模块设计。LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;USEIEEE_NUMERIC_STD.ALL;USEIEEE.STD_LOGIC_ARITH.ALL;USEIEEE.STD_LOGIC_UNSICNED.ALL;USEWORK.alucoder.ALL;ALUsalu_comandcyAcccoutover

ENTITYaluISPORT(s:INSTD_LOGIC_VECTOR(7DOWNTO0);cy:INSTD_LOGIC;alu_comand:INSTD_LOGIC_VECTOR(2DOWNTO0);Acc:INOUTSTD_LOGIC_VECTOR(7DOWNTO0);cout,over:BUFFERSTD_LOGIC);ENDalu;ARCHITECTUREalgOFaluISSIGNALr1,s1,f1:STD_LOGIC_VECTOR(8DOWNTO0);BEGINr1<="0"&Acc;s1<="0"&s;PROCESS(r1,s1,cy,alu_comand)BEGINCASEalu_comandIS

WHENadd=>f1<=r1+s1;WHENaddc=>IFcy="0"THENf1<=r1+s1;ELSEf1<=r1+s1+1;ENDIF;WHENsub=>f1<=r1+NOT(s1)+1;WHENsubc=>IFcy="0"THENf1<=r1+NOT(s1)+1;ELSEf1<=r1+NOT(s1);ENDIF;WHENnot=>f1<=NOT(r1);WHENand=>f1<=r1ANDs1;WHENor=>f1<=r1ORs1;WHENXOR=>f1<=r1XORs1;WHENOTHERS=>f1<="-";

ENDCASE;ENDPROCESS;Acc<=f1(7DOWNTO0);cout<=f1(8);over<=f1(8)XORf1(7);ENDalu;

4.2时序逻辑电路设计4.2.1触发器1.D触发器LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYdffISPORT(d,clk:INSTD_LOGIC;q:OUTSTD_LOGIC);ENDdff;ARCHITECTURErtl_ifOFdffISBEGINPROCESS(clk)BEGIN

IF(clk"EVENT"ANDclk=1)THENq<=d;ENDIF;ENDPROCESS;ENDrtl_if;结构体的另一种描述如下:ARCHITECTURErtl_waitOFdffISBEGINPROCESSBEGINWAITUNTILclk"EVENTANDclk=1;q<=d;ENDPROCESS;ENDrtl_wait;

4.2.3寄存器D0~D7:8位并行数据输入端。SI:串行数据输入端。Q7:串行数据输出端。Q0~Q6:内部寄存器数据输出端。clk:时钟。ckin:时钟信号禁止,只有当其无效时,移位寄存器才在时钟的触发下进行移位操作。S/L:移位(shift)/装入(load)。当此端为高电平时,可执行移位操作,当此端为低电平时,读入D0~D7端的并行数据。CLR:异步清零。D[7:0]SIS/LQ7clkckinclr

串/并入、串出移位寄存器LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYshifterISPORT(clr,si,ckin,clk:INSTD_LOGIC;d:INSTD_LOGIC_VECTOR(7DOWNTO0);q:OUTSTD_LOGIC);sl:INBIT);ENDshifter;ATCHITECTURErtl_shifterOFshifterISSIGNALtemp8:STD_LOGIC_VECTOR(7DOWNTO0);BEGIN

PROCESS(clr,sl,ckin,clk)IF(clr="0")THENtemp8<="00000000";q<=temp8(7);ELSIF(clk"EVENT)AND(clk="1")AND(ckin="0")THENIF(sl="0")THENtemp8<=d;--装入数据q<=d(7);ELSEq<=temp8(7);temp8(7)<=temp8(6);temp8(6)<=temp8(5);

temp8(5)<=temp8(4);temp8(4)<=temp8(3);temp8(3)<=temp8(2);temp8(2)<=temp8(1);temp8(1)<=temp8(0);temp8(0)<=si;ENDIF;ENDIF;ENDPROCESS;ENDrtl_shifter;

4.2.4计数器8位异步计数器的设计Q/QDclkQ/QDclkQ/QDclkQ/QDclkdclkclrcount_in(0)count_in(1)count_in(8)Q0Q1Q2Q7

计数器的顶层设计LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYriplecountISPORT(clk,clr:INSTD_LOGIC;count:OUTSTD_LOGIC_VECTOR(7DOWNTO0));ENDriplecount;ARCHITECTURErtl_riplecountOFriplecountISSIGNALcount_in:STD_LOGIC_VECTOR(8DOWNTO0);

COMPONENTdfftPORT(clk,clr,d:INSTD_LOGIC;Q:OUTSTD_LOGIC;Qn:BUFFERSTD_LOGIC);ENDCOMPONENT;--调用当前库中的同名实体作为元件BEGINcount_in(0)<=clk;genl:FOR:IN0TO7GENERATEU:dfftPORTMAP(clk=>count_in(i),clr=>clr;d=>count_in(i+1),,Q=>count(i);Qn=>count_in(i+1));ENDGENERATE;ENDrt_riplecountl;

--单个触发器性能描述LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYdfftISPORT(clk,clr,d:INSTD_LOGIC;Q:OUTSTD_LOGIC;Qn:BUFFERSTD_LOGIC);ENDdfft;ARCHITECTURErtldOFdfftISBEGIN

PROCESS(clk,clr)BEGINIF(clr="0")THENQ<="0";Qn<="1";ELSIF(clk"EVENTANDclk="1")THENQ<=d;Qn<=NOTd;ENDIF;ENDPROCESS;ENDrtld;

4.3存储器4.3.1概述存储器单元实际上是时序逻辑电路的一种。按存储器的使用类型可分为只读存储器(ROM)和随机存取存储器(RAM),两者的功能有较大的区别,因此在描述上也有所不同。存储器是许多存储单元的集合,按单元号顺序排列。每个单元由若干二进制位构成,以表示存储单元中存放的数值。这种结构和数组的结构非常相似,故在VHDL语言中,通常由数组描述存储器。

TYPEmemoryISARRAY(INTEGERRANGE<>)OFINTEGER;TYPEwordISSTD_LOGIC_VECTOR(k-1DOWNTO0);TYPEmemoryISARRAY(0TOw-1)OFword;

4.3.3随机存储器RAMLIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;USEIEEE.STD_LOGIC_ARITH.ALL;ENTITYram4kISGENERIC(k:INTEGER:=8;w:INTEGER:=12;rd_del,wr_del:TIME);PORT(WR,RD,CS:INSTD_LOGIC;Adr:INSTD_LOGIC_VECTOR(w-1DOWNTO0);D:INOUTSTD_LOGIC_VECTOR(k-1DOWNTO0));ENDram4k;WRRDCSAdr[11:0]Dout[7:0]

ARCHITECTUREbehavram4kOFram4kISTYPEmemoryISARRAY(0TO2**w-1)OFSTD_LOGIC_VECTOR(k-1DOWNTO0);SIGNALsram:memory;SIGNALAdr_in:INTEGER;BEGINAdr_in<=CONV_INEGER(Adr);--位矢量转换成整数PROCESS(WR,RD,CS)BEGIN

IFCS="0"THENIFRD="0"THEND<=sram(Adr_in)AFTERrd_del;ELSIFWR="0"THENsram(Adr_in)<=DAFTERwr_del;ENDIF;ELSED<=(OTHERS’Z’)AFTERrd_del;ENDIF;ENDPROCESS;ENDbehav;

4.3.2只读存储器ROM在用VHDL语言描述ROM时,ROM的内容应在仿真时先读到ROM中,这就是ROM的初始化。存储器的初始化要依赖于外部文件的读取,即由TEXTIO对ROM进行初始化。下面是对ROM进行初始化的实例。VARIABLEstartup:BOOLEAN:=TRUE;VARIABLEl:LINE;--LINE是在TEXTIO程序包定义的存取类型VARIABLEj:INTEGER;VARIABLErom:memory;FILEromin:TEXTISIN"rom2k.in";--TEXT是在TEXTIO程序包定义的文件类型

初始化程序:IFstartupTHENFORjINrom‘RANGELOOP--利用数据区间属性函数获得数组的上下限READLINE(romin,l);--从文件romin中读入一行放入l中。READ(l,rom(j));--从l中读入一个数据放入rom中ENDLOOP;ENDIF;G1G2Adr[11;0]Dout[7:0]

只读存储器ROM的VHDL程序。LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;USEIEEE.STD_LOGIC_ARITH.ALL;USESTD.TEXTIO.ALL;ENTITYrom4kISPORT(G1,G2:INSTD_LOGIC;Adr:INSTD_LOGIC_VECTOR(11DOWNTO0);dout:OUTSTD_LOGIC_VECTOR(7DOENTO0);ENDrom4k;

ARCHITECTUREbehav_rom4kOFrom4kISTYPEwordISSTD_LOGIC_VECTOR(7DOWNTO0);TYPEmemoryISARRAY(0TO4095)OFword;SIGNALadr_in:INTEGERRANGE0TO4095;VARIBLErom:memory;VARIBLEstartup:BOOLEAN:=TURE;VARIBLEl:LINE;VARIBLEj:INTEGER;FILEromin:TEXTISIN“rom2k.in”;--文件类说明.BEGINPROCESS(G1,G2)BEGIN

IFstartupTHENFORjINrom"RANGELOOPREADLINE(romin,l);READ(l,rom(j));ENDLOOP;startup:=FALSE;ENDIF;adr_in<=CONV_INTEGER(Adr);--将位矢量转换成整数.IF(G1="1"ANDG2="1")THENdout<=rom(adr_in);ELSEdout<="ZZZZZZZZ”;ENDIF;ENDPROCESS;ENDbehav_rom2k;

4.3.4先进后出堆栈先进后出堆栈是处理程序中断的常用数据结构,其数据存放结构和RAM是一致的,但存储方式有所不同。先进后出堆栈由2个功能块组成,即存储器体和堆栈指针SP,进堆时SP+1→SP指向下一个存储单元;出堆时SP-1→SP,并把SP所指示的存储单元的内容输出。din[7:0]pushpopclkresetDout[7:0]

256字节先进后出堆栈的VHDL程序。LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;USEIEEE.STD_LOGIC_ARITH.ALL;USEIEEE.STD_LOGIC_UNSIGNED.ALL;ENTITYstackISGENERIC(w:INTEGER:=256;k:INTEGER:=8);PORT(clk,reset,push,pop:INSTD_LOGICdin:INSTD_LOGIC_VECTOR(k-1DOWNTO0);dout:OUTSTD_LOGIC_VECTOR(k-1DOWNTO0));ENDstack;

ARCHITECTUREbehav_stackOFstackISTYPEmemoryISARRAY(0TOw-1)OFSTD_LOGIC_VECTOR(k-1DOWNTO0);SIGNALram:MEMORY;SIRNALsp:INTEGERRANGE0TOw-1;BEGINdout<=ram(sp);P1:PROCESS(clk)BEGINIF(clk"EVENTANDclk="1")THENIF(push="0")THENram(sp)<=din;ENDIF;ENDIF;ENDPROCESSP1;数据堆栈写

P2:PROCESS(clk,reset)BEGINIF(reset="1")THENsp<=0;ELSIF(clk"EVENTANDclk="0"ANDpush=’0’)THENsp<=sp+1;--在clk的后沿sp+1ElSIF(clk"EVENTANDclk="1"ANDpop=’0’)THENsp<=sp-1;--sp指针修改ENDIF;ENDPROCESSP2;ENDbehav_stack;加减计数器操作

4.4有限状态机有限状态机是时序电路的通用模型,任何时序电路都可以表示为有限状态机。对于大部分数字电子系统,都可以划分为控制单元和数据单元两个组成部分,控制单元的主体是一个有限状态机,它接收外部信号和数据单元产生的状态的信息,产生各种控制信号,决定何时进行何种数据处理。有限状态机分为两类:Moore型和Mealy型。次态逻辑状态寄存器输出逻辑输入次态现态输出

状态机的设计步骤定义状态机的各状态。适当地确定状态机的工作状态,是状态机设计的基础,需要充分利用设计者的设计经验。建立状态转换图。构造状态转换图时,通常从一个比较容易的状态开始。例如系统的初始状态、复位状态或空闲状态等,都是很好的起始状态。为每个状态标出转换的条件,相应的输入、输出信号。建立状态机进程。在VHDL程序中,通常用进程描述有限状态机。由于次态是现态及输入信号的函数,因此,往往将现态和输入信号作为进程的敏感信号。进程中定义状态的转移。所有的状态均可表达为CASE_WHEN结构中的一条CASE语句,利用CASEWHEN语句IF_THEN_ELSE语句实现状态的转移。

存储器控制器的设计存储器控制器的输入信号是微处理器的就绪ready和读写信号read_write。当上电复位或者ready有效时,存储器控制器开始工作,并在下一个时钟周期判断本次作业任务是读存储器还是写存储器,当read_write=‘1’时为读操作,使OE和CS信号有效,read_write=‘0’时为写操作,WE和CS信号有效。当ready信号再次有效时,结束本次读写操作,并使控制器返回到初始状态。存储器控制器readyread-writeOEWECS

存储器控制器状态转移图状态图decisionidlewritereadreadyreadyreadyreadyreadyreadyread_writeread_write

带异步复位的双进程状态机的存储器控制器设计。LIBRARYIEEEUSEIEEE.STD_LOGIC_1164.ALL;ENTITYmemoy_controllerISPORT(reset,read_write,ready,clk:INSTD_LOGIC;OE,WE,CS:OUTSTD_LOGIC);ENDmemory_controller;ARCHITECTUREstate_machineOFmemory_controllerISTYPEstatetypeIS(idle,decision,read,write);SIGNALpresent_state,next_state:STATETYPE;

带异步复位的双进程状态机的存储器控制器设计。state_comb:PROCESS(reset,present_state,read_write,ready)BEGINIF(reset="1")THENnext_state<=idle;OE<="0";WE<="0";CS<=‘0’;ELSECASEpresent_stateIS

WHENidle=>OE<="0";WE<="0";CS<="0";IFready="1"THENnext_state<=decision;ELSEnext_state<=idle;ENDIF;WHENdecision=>OE<="0";WE<="0";CS<="0";IF(read_write="1")THENnext_state<=read;ELSEnext_state<=write;ENDIF;

WHENread=>OE<="1";WE<="0";CS<=‘1";IF(ready="1")THENnext_state<=idle;ELSEnext_state<=read;ENDIF;WHENwrite=>OE<="0";WE<="1";CS<=‘1";IF(ready="1")THENnext_state<=idle;ELSEnext_state<=write;ENDIF;

WHENOTHERS=>OE<=‘0’;WE<=‘0’;CS<=‘0’;next_state<=idle;ENDCASE;ENDIF;ENDPROCESSstate_comb;

state_clocked:PROCESSBEGINWAITUNTILclk"EVENTANDclk="1";present_state<=next_state;ENDPROCESSstate_clocked;ENDstate_machine;PROCESS(1)CASE-WHENIF-THEN-ELSEPROCESS(2)WAITUNTILclk‘EVENTANDclk=‘1’输入次态现态

第二节国际租赁合同与租金承租人供货商出租人金融机构1选定租赁物5交付租赁物2预约租赁3签订租赁合同7支付租金4订购设备6支付货款提供贷款还本付息63

一、国际租赁合同国际租赁合同属于经济合同的范畴,是出租人和承租人为租赁一定资产而明确相互权利和义务的契约文件。由于国际租赁业务本身的特殊性,一笔国际租赁业务涉及多方当事人和多笔业务,因此与租赁业务有关的合同包括进出口购销合同、国际租赁合同、贷款合同等多项合同。其中,租赁合同是最基本的合同。64

国际租赁合同国际租赁合同的内容往往根据不同的租赁方式而有所差异。国际租赁合同包括一般性条款和专业特殊性条款两类法律条款。下面以融资性租赁为例。65

一、租赁合同的一般性条款1.合同说明条款1)确定合同性质;2)叙明合同当事人的名称住所;3)标明合同签订的日期地点4)说明出租人应承租人的要求购进经承租人选定的设备,按照双方商定的条款租赁给承租人使用.66

2合同实施的前提条件条款有些合同规定了实施合同的前提条件条款.此类合同虽经当事人签字,但必须在履行了前提条件或生效条款后方能生效.租赁合同实施的一般前提条件:项目批准文件,进口许可证,偿还租金保证函67

3租赁设备条款租赁设备的名称,制造厂家,出厂日期,规格,型号,数量,设备的技术性能,交货地点和使用地点等写明.可另具附表祥列.68

4租赁设备的交货与验收条款承租人确认出租人与供货人之间有关进口销售合同中的租赁设备是承租人根据自己的需要所选定的;承租人须向出租人提供出租人认为必要的各种证明.交付人不能按时交付租赁设备应付的责任验收的有关事项.69

5税款费用条款租赁交易中涉及的进口关税,进口工商税,海关规定的增殖税等税款和费用,如果未作其他规定,则应由承租人支付.70

6租期和起租日条款租期即合同有效期或承租人使用租赁设备的基本期限,其长短可由当事双方协商而定.基本租期、续租租期。起租日就是租金开始计算日,一般有付款日交货日等几种计算方法.71

7租金支付条款必须明确规定,除非因出租人的过错,承租人有义务按合同规定向出租人支付租金.支付方式协商而定支付货币72

二、租赁合同的特殊性条款1购货合同与租赁合同的关系条款2租赁设备的所有权条款和使用权条款3承租人不得中途解约条款4对出租人负责和对承租人保障条款5对承租人违约和对出租人补救条款6租赁设备的使用、保管、维修和保养条款7保险条款8租赁保证金和担保条款73

9租赁设备租赁期满的处理条款10对第三方的责任条款11转租赁条款12租赁债权的转让和抵押条款13预提所得税条款14争议解决条款74

预提所得税外国企业在中国境内未设立机构、场所或者虽设有机构、场所,但与该机构、场所没有实际联系,而有取得的来源于中国境内的利润(股息、红利)、利息、租金、特许权使用费和其它所得,均应就其收入全额(除有关文件和税收协定另有规定外)征收预提所得税。按预提方式,即由所得支付人(付款人)在向所得受益人(收款人)支付所得(款项)时为其代扣代缴税款,课税的一种个人所得税或公司所得税。75

二、国际租赁的租金现代租赁是出租者与承租者之间的一种商品交换关系,是承租者为了取得租赁资产使用权与出租者之间的一种有代价的交换行为,即出租者让渡资产的使用价值,承租者支付给出租者等价物-----租金。因此租金就是承租者为取得出租者的租赁资产经营权或使用权而支付给出租者的费用。租金是签订租赁合同的一项主要内容。租金的高低,直接关系到出租与承租双方的经济利益。76

出租者要从取得的租金中,得到出租资产的补偿和收益,即要收回租赁资产的购进原价,贷款利息、营业费用和一定利润;承租者要比照租金核算成本,即租赁资产所生产的产品的收入,除抵偿租金外,还要取得一定的利润。77

(一)租金的构成要素根据国际租赁的实践,现代租赁的租金一般由下列几个因素构成:1、购买租赁资产的货款租赁公司根据承租者的要求出资购置设备而发生的费用构成购置租赁资产的成本。购买租赁组成的货款一般包括购置租赁资产的货价、运输费、途中保险费78

注意:如果设备是进口的,设备货款则分为以下三种情况:1)设备进口价为运输保险在内价(CIF),则以CIF价格为设备货款;2)设备进口价为运费在内价(CFR),则以CFR价格加途中保险费为设备货款;3)设备进口价为离岸价格(FOB),则以FOB价格加运输费和途中保险费为设备货款;总之,凡由租赁公司垫付的运费和保险费,均应包括在设备货款中;凡由承租者直接支付的运输费和保险费,在计算租金时应予以扣除。79

2预计的名义货价也叫设备残值,是指租赁物件在租赁期满后预计的市场价值。设备残值依租赁资产的种类、性能和市场需求等条件而各不相同。设备残值高意味着租金低,有利于承租者;设备残值少意味着租金高,有利于出租者。80

3利息购买设备的银行贷款利息,是指出租者为承租者购置租赁设备向银行支付的贷款利息。一般而言,租赁公司的租赁资本可以有多种来源,不同资产来源决定了利息的多少,从而影响了资金筹措的成本。资金的来源不同,利率水平亦不同。81

4租赁手续费也叫初期费用,是指出租者为承租者办理租赁资产所开支的营业费用(如办公费工资旅差费保险费税金等)租赁手续费根据租赁项目的不同和市场供需情况的不同而变化.至于收取多少手续费,在计算租金时如何处理,各租赁公司的规定不尽相同.租赁手续费高,有利于出租者;租赁手续费低,有利于承租者.82

说明:以上4个因素,购买租赁资产的货款预计的名义货价利息租赁手续费构成了租金的主体.由于租金不是一次付给,而是采取期限分额支付的办法,根据现值理论,不同时期支付的款项具有不同的现值,因此,租赁期限会影响租金的现值.83

5租赁期限租赁期限的长短主要取决于租赁设备的法定折旧年限和经济寿命.对于出租者来说,由于技术不断进步,为避免设备提前淘汰而遭受损失,因此愿意采取加速折旧的办法,把设备前期出租的租金定的较高;承租者则希望租赁期限长些,宁肯多付利息,而争取把租金支付次数增多.国际租赁期限通常为3至5年,大型设备稍长一些.84

租金的构成要素从前述可知,在租金的各项组成中,租赁设备的购价事先已定,因此租金的高低主要取决于利息、手续费和估计残值的多少。对承租人而言,如何提高残值和把利息、手续费降到最低限度是减低租金的关键。85

(二)租金的计算1.平均分摊法此种方法是一种租赁成本计算法,计算公式为:租金=(购买租赁资产的货价—预计设备残值+利息+手续费)/租赁期限86

例题一例:某项租赁业务,租赁物件的货价为100万元,租赁期为5年,分5次支付租金,年利率为5%,残值部分为16000元,手续费为15000元,计算每期应付租金额.每期应付租金额=[(1000000-16000)+276000+15000]/5=255000(元)87

2递减式计算法适用于承租人所交的租金中,每期偿还的本金相等,但其中所含的利润费不同,即开始所付的租金高,而后几年递减.计算公式为:租金=各期占款本金数×年利率×占款年数+各期应还本金数88

例题二某企业与某租赁公司达成一笔设备租赁业务,设备的概算成本为300万元,租期为5年,每年年末支付一次租金,利息和手续费折合年利率为9%,如果采用先期多付,后期少付的办法,每年应付的租金,5年应付的总租金,每年的利费额和5年的利费额分别是多少?89

计算:第一年应付租金为:300万×9%×1+60万=87万第二年应付租金为:240万×9%×1+60万=81.6万第三年应付租金为:180万×9%×1+60万=76.2万第四年应付租金为:120万×9%×1+60万=70.8万第五年应付租金为:60万×9%×1+60万=65.4万5年共交租金:87+81.6+76.2+70.8+65.4=381万元90

第一年至第五年的利费额分别为27万、21.6万、16.2万、10.8万和5.4万。5年的利费总额为381万元—300万元=81万元。91

作业1:由于设备改造需要,中北机械设备制造股份有限公司将以融资租赁方式引进一套成套设备。该设备的货价为1000万美元,租赁期为1999年1月1日---2003年12月1日,于每年年末支付租金,年利率为5%,估计到期残值为16万美元,手续费为1.5%。问:每期租金为多少?92

作业2:某企业欲从某国外租赁公司租进一套设备,该设备的概算成本为260万元,租期为4年,每年年末支付租金,如利息和手续费折合年利率为5%,采用递减式计算方法,则每年应付的租金是多少?4年应付的总租金,每年的利费额和4年的利费额分别是多少?93'

您可能关注的文档

- [整理]城市空间结构(1)课件PPT.ppt

- [整理]城市空间结构课件PPT.ppt

- [整理]基因工程的应用自制课件PPT.ppt

- [整理]基因工程的基本操作程序教学课件PPT课件.ppt

- [整理]基于标准的教学与教学设计(精)课件PPT.ppt

- [整理]基础免疫学课件(1)课件PPT.ppt

- [整理]基础会计学课件——帐户的分类课件PPT.ppt

- [整理]基础会计(利润形成和分配的核算)课件PPT.ppt

- [整理]基础仪表培训教材课件PPT.ppt

- [整理]境外所得税抵扣明细表课件PPT.ppt

- [整理]塞下曲-卢纶新课件PPT.ppt

- [整理]复发性静脉曲张1.9课件PPT.ppt

- [整理]复习课第2节-动物运动的形成-(共33张PPT)课件PPT.ppt

- [整理]备自投方式培训课件PPT.ppt

- [整理]备考2019中考初中九年级数学-答题技巧大全课件PPT.ppt

- [整理]外径千分尺读数课件PPT.ppt

- [整理]外用药物集锦(一)(2)课件PPT.ppt