- 2.83 MB

- 2022-04-29 14:47:59 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

'基于FPGA的DSP开发设计精要

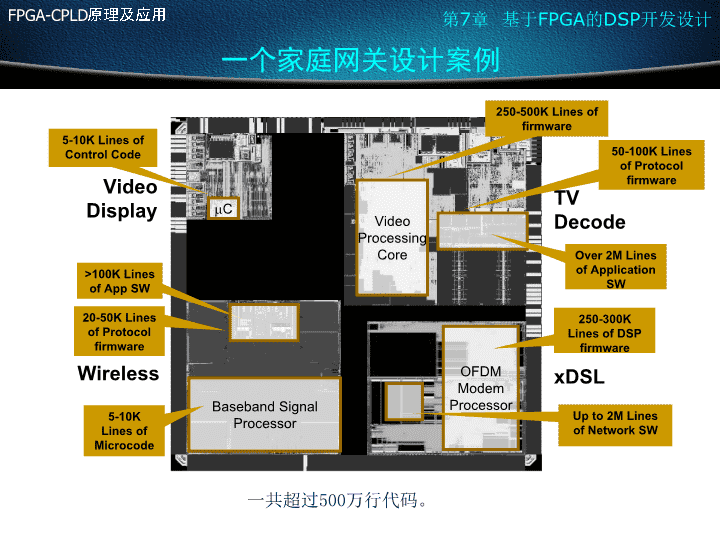

一个家庭网关设计案例Video

DisplayTVDecodeWirelessxDSLmCVideoProcessingCoreBasebandSignal

ProcessorOFDM

Modem

Processor5-10KLinesofMicrocode>100KLinesofAppSW20-50KLinesofProtocolfirmware5-10KLinesofControlCode250-500KLinesoffirmwareOver2MLinesofApplicationSW50-100KLinesofProtocolfirmware250-300KLinesofDSPfirmwareUpto2MLinesofNetworkSW一共超过500万行代码。

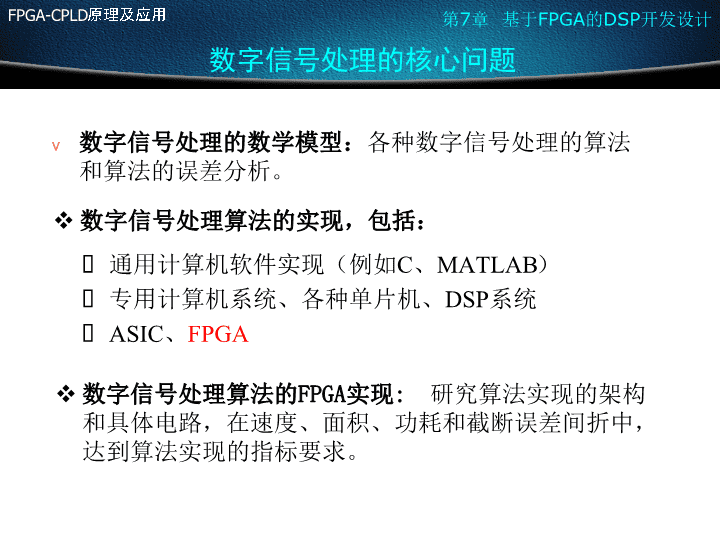

数字信号处理的核心问题数字信号处理的数学模型:各种数字信号处理的算法和算法的误差分析。数字信号处理算法的实现,包括:通用计算机软件实现(例如C、MATLAB)专用计算机系统、各种单片机、DSP系统ASIC、FPGA数字信号处理算法的FPGA实现:研究算法实现的架构和具体电路,在速度、面积、功耗和截断误差间折中,达到算法实现的指标要求。

例如:Matlab、C语言或其它语言编程。DSP工具软件,如simulink的信号处理仿真。缺点:成本高、处理速度受限,体积大。优点:用户的图形界面友好。应用:对于人机交互有较高要求的系统,体积不敏感的应用。数字信号处理仿真。数字信号处理的实现方案一在通用PC上利用软件实现

单片机运算速度也在提高,可以实现速度要求不高或简单的信号处理算法。缺点:速度慢(尤其是乘法慢)、实时性差;优点:价格低廉;应用:计算简单的工业控制现场等。数字信号处理的实现方案二单片机实现

目前多采用RISC和改进的哈佛结构,专门的数据管理;内部有硬件乘法累加器,使乘加运算变得简单。流水线操作(pipeline)速度快,是现在的主流方法。优点:速度快、实时性好,价格合理,使用灵和;缺点:串行运算,还不能满足极高速的运算处理;应用:广泛应用于军事、民用电子等几乎所有电子领域。数字信号处理的实现方案三利用通用可编程DSP芯片来实现

直接面向特定应用的ASIC芯片,如MP3系统。直接面向特定应用的SoC,如将DSP核从传统的通用型处理器中分离出来,面向特定应用对象增加外部电路或MCU构成SOC。如DSP+ARM的双核SoC器件。优点:速度快、特定应用性能好,大批量时价格最低;缺点:面向特定应用优化。应用:广泛应用于民用电子领域,适于大批量产品。数字信号处理的实现方案四ASIC和片上系统SoC实现

近年来,随着FPGA技术的发展,其实现DSP算法的能力越来越强,性价比不断提高,逐步在批量产品中得到应用。特别是SOPC技术的发展,使FPGA正在逐步成为新一代的DSP系统实现方法,与DSP形成互补。优点:易于实现并行处理,速度快;可重构硬件,使用灵活,可按需设计,性价比不断提高。缺点:目前开发较难。应用:高端应用,并逐步用于军事、民用电子等几乎所有电子领域。数字信号处理的实现方案五利用FPGA等可编程逻辑阵列实现

CPU定制硬件通用DSP专用DSP/CPU通用CPU可配置处理器性能功耗灵活性单位成本初始成本ASICASSPFPGA

第7章基于FPGA的DSP开发设计在基于FPGA的DSP开发中,Altera提出了基于FPGA的DSP开发平台。由Altera与其合作伙伴AMPP(AlteraMegafunctionPartnerProgram)提供了针对DSP设计的各种用于硬件加速的IP核。每一个核都可以进行参数设置,以构成针对特定应用的硬件功能模块。

内容与要点主要内容:DSPBuilder工具介绍;设计流程;设计规范;模块库;设计实例。本章要点:DSPBuilder设计流程、规范;Simulink模型仿真;利用MATLAB建模工具和DSPBuilder开发环境,认识如何将算法级仿真向硬件模块实现过渡的设计过程。

SOPC技术开发套件1)QuartusⅡ9.1SP22)SOPCBuilder6.03)NiosⅡIDE6.04)DSPBuilder6.05)Matlab2008a

StateflowStateflowStateflowBlocksetsCodeGeneration,RTW,SFCoderToolboxesDesktopApplicationsAutomatedReportsDAQcardsInstruments*SlideCourtesyofTheMathWorksMATLAB

HDLSynthesisVerifyinHardwarePlaceandRouteCreatesSimulationTestbenchDSPBuilderCreatesHDLCodeDownloadDesigntoDSPDevelopmentKitsCreatesSOPCBuilderReadyComponent

基于FPGA的DSP开发技术MATLAB/DSPBuilder软件DSPBuilder简介基于DSPBuilder的DSP模块开发流程正弦发生器模块设计实例DSPBuilder层次性设计FIR数字滤波器设计实例层次性设计方法FDATool使用利用MegaCore的设计

基于FPGA的DSP开发技术MATLAB/DSPBuilder软件DSPBuilder简介基于DSPBuilder的DSP模块开发流程正弦发生器模块设计实例DSPBuilder层次性设计FIR数字滤波器设计实例层次性设计方法FDATool使用利用MegaCore的设计

基于FPGA的DSP开发技术DSPBuilder是一个系统级(算法级)设计工具实现了系统级(算法仿真建模)到RTL级(硬件实现)无缝过渡DSPBuilder简介

基于FPGA的DSP开发技术利用DSPBuilder进行DSP模块设计是SOPC技术的重要组成部分:一方面,由Matlab/DSPBuilder和QuartusII软件工具开发的DSP模块可以成为FPGA电路系统的组成部分;另一方面,可以通过Matlab/DSPBuilder为NiosII嵌入式处理器设计各类加速器,并以指令的形式加入到NIOSII的指令系统,成为NiosII系统的接口设备。DSPBuilder简介

基于FPGA的DSP开发技术MATLAB/DSPBuilder软件DSPBuilder简介基于DSPBuilder的DSP模块开发流程正弦发生器模块设计实例DSPBuilder层次性设计FIR数字滤波器设计实例层次性设计方法FDATool使用利用MegaCore的设计

基于FPGA的DSP开发技术第五步:设计编译和下载在QuartusII中编译用户的设计,最后将设计下载,进行测试验证。第二步:转化模型文件到硬件描述语言文件利用SignalCompiler模块完成模型文件到硬件描述语言文件的转换,转换之后的HDL文件是RTL级(寄存器传输级,可综合的格式)。第三步:RTL级仿真DSPBuilder支持自动流程的ModelSim仿真。用户也可以利用第二步产生的HDL文件使用其它的仿真工具手动地进行仿真。第四步:RTL级综合、网表产生、适配、时序仿真自动流程中可以选择让DSPBuilder自动调用QuartusII等EDA软件来完成相应的工作;手动流程允许用户选择相应的软件来完成相应的工作,手动流程需要更多的干预,同时提供了更大的灵活性,用户可以指定综合、适配等过程的条件。为确定RTL级适配后的网表与Simulink中建立的DSP模型的一致性,需要进行时序仿真第一步:完成设计输入和模型仿真利用Matlab/Simulink进行设计输入,在Matlab/Simulink中建立一个模型文件(mdl文件),调用DSPBuilder和其它Simulink库中的模块,构成系统级或算法级设计框图。利用Simulink的图形化仿真、分析功能,分析设计模型的正确性,完成模型仿真。该步设计跟一般的Matlab/Simulink建模仿真没区别第三步:RTL级仿真DSPBuilder支持自动流程的ModelSim仿真。用户也可以利用第二步产生的HDL文件使用其它的仿真工具手动地进行仿真。第四步:RTL级综合、网表产生、适配、时序仿真自动流程中可以选择让DSPBuilder自动调用QuartusII等EDA软件来完成相应的工作;手动流程允许用户选择相应的软件来完成相应的工作,手动流程需要更多的干预,同时提供了更大的灵活性,用户可以指定综合、适配等过程的条件。为确定RTL级适配后的网表与Simulink中建立的DSP模型的一致性,需要进行时序仿真第三步:RTL级仿真DSPBuilder支持自动流程的ModelSim仿真。用户也可以利用第二步产生的HDL文件使用其它的仿真工具手动地进行仿真。第四步:RTL级综合、网表产生、适配、时序仿真自动流程中可以选择让DSPBuilder自动调用QuartusII等EDA软件来完成相应的工作;手动流程允许用户选择相应的软件来完成相应的工作,手动流程需要更多的干预,同时提供了更大的灵活性,用户可以指定综合、适配等过程的条件。为确定RTL级适配后的网表与Simulink中建立的DSP模型的一致性,需要进行时序仿真第三步:RTL级仿真DSPBuilder支持自动流程的ModelSim仿真。用户也可以利用第二步产生的HDL文件使用其它的仿真工具手动地进行仿真。基于DSPBuilder的DSP模块开发流程

基于FPGA的DSP开发技术MATLAB/DSPBuilder软件DSPBuilder简介基于DSPBuilder的DSP模块开发流程正弦发生器模块设计实例DSPBuilder层次性设计FIR数字滤波器设计实例层次性设计方法FDATool使用利用MegaCore的设计

一个简单的正弦波发生器,主要由四个部分构成。InCount是阶梯信号发生模块,产生一个按时钟线性递增的地址信号,送往SinLUT。SinLUT是一个sin(正弦函数)值的查找表(LUT:LookUpTable)模块,由递增的地址获得正弦波的量化值输出,输出的8位正弦波数据经延时模块Delay后送往Product乘法模块,与SinCtrl相乘。SinCtrl是1bit输入,SinCtrl通过Product就完成了对有无正弦波输出的控制。SinOut是整个正弦波发生器模块的输出,送往D/A即可获得正弦波的输出(模拟信号)。基于FPGA的DSP开发技术

基于FPGA的DSP开发技术乘法模块一位输入,控制正弦波的有无正弦波发生器模块的输出阶梯信号发生模块,产生一个按时钟线性递增的地址信号正弦函数值的查找表模块,由递增的地址获得正弦波的离散值输出延时模块正弦发生器模块设计实例

基于FPGA的DSP开发技术第一步:利用Simulink建立模型文件1)运行Matlab,建立工作目录,启动Simulink,新建模型文件2)放置SignalCompiler:单击Simulink库列表中的AlteraDSPBuilder,单击Altlab项,选中SignalCompiler组件,按住鼠标左键拖放到新模型窗口中。SignalCompiler是任何DSP系统设计必须要添加的模块正弦发生器模块设计实例

基于FPGA的DSP开发技术

基于FPGA的DSP开发技术第一步:利用Simulink建立模型文件3)添加IncrementDecrement模块。IncrementDecrement模块是DSPBuilder库中Arithmetic子库中的模块。4)设置IncrementDecrement模块。修改模块的命名;双击模块进入模块参数设置对话框。正弦发生器模块设计实例

基于FPGA的DSP开发技术总线类型:有符号整数有符号小数无符号整数总线位宽增减方向初始值是否使用控制输入选项时钟相位选择采样时间设置

基于FPGA的DSP开发技术第一步:利用Simulink建立模型文件5)添加正弦查找表。在Gate&Control子库中找到查找表模块LUT,把LUT拖放到新建模型窗口,将LUT模块的名字修改为“SinLUT”。6)设置正弦查找表模块参数。双击模块进入模块参数设置对话框。正弦发生器模块设计实例

基于FPGA的DSP开发技术总线类型:有符号整数有符号小数无符号整数输出位宽查找表地址查找表内容计算式选中”UseLPM”选项,QuartusII将利用目标器件中的嵌入式RAM构成SinLUT选中”RegisterAddress”选项会生成输入地址总线。若目标器件是Straitix或者Cyclone,并且选中了LPM选项,用户必须选中”RegisterAddress”选项

基于FPGA的DSP开发技术第一步:利用Simulink建立模型文件7)添加Delay模块。选中Storage子库下的Delay模块,拖放到新建模型窗口。设置延迟的周期数时钟相位选择正弦发生器模块设计实例

基于FPGA的DSP开发技术第一步:利用Simulink建立模型文件8)添加Product(乘法)模块。在AlteraDSPBuilder库中选择Arithmetic子库,找到Product模块。设置乘法模块采用的流水线级数使用参数化模块库实现使用FPGA的专用模块实现正弦发生器模块设计实例

基于FPGA的DSP开发技术第一步:利用Simulink建立模型文件9)添加端口SinCtrl。在IO&BUS子库,找到AltBus模块,拖放到新建模型窗口中,修改AltBus模块的名字为SinCtrl。10)添加端口OUT。在IO&BUS子库,找到AltBus模块,拖放到新建模型窗口中,修改AltBus模块的名字为Out。正弦发生器模块设计实例

基于FPGA的DSP开发技术选中Saturate选项,则当输出大于最大正值或小于最小负值时,则输出被强制为最大正值或最小负值。

基于FPGA的DSP开发技术保存文件,完成第一步模型文件的建立进行第二步——模型仿真

基于FPGA的DSP开发技术第二步:利用Simulink进行模型仿真需要添加激励信号和观察模块1)添加Step模块加入一个Step(阶跃模块),模拟SinCtrl的按键使能操作。在Simulink基本库中选择Source子库,把Step模块拖放到Sinout模型窗口中。2)添加波形观察模块Scope在Simulink基本库中选择Sinks子库,把Scope(示波器)模块拖放到SinOut模型窗口中。模型仿真用的来自AlteraDSPBuilder库外的模块,SignalCompiler不能将其转换成硬件描述语言正弦发生器模块设计实例

基于FPGA的DSP开发技术设置Scope模块的波形观察窗口数

基于FPGA的DSP开发技术正弦发生器模块设计实例第二步:利用Simulink进行模型仿真3)设置仿真激励信号。在SinOut模型中,只有一个输入端口SinCtrl,需要设置与之相连的Step模块,双击Step模块,在弹出的Step模块参数设置对话框中设置对其输入端口SinCtrl施加的激励。

基于FPGA的DSP开发技术阶跃时刻(Steptime):Step模块的输出在该时刻发生阶跃,默认值为1,单位为秒。初始值(Initialvalue):在阶跃时刻的之前的Step模块的输出值,默认值为0。终值(Finalvalue):在阶跃时刻之后Step模块的输出值,默认值为1。采样时刻(Sampletime):Step模块输出的采样频率,设为0,设成0进行连续采样;设成1只在大的时间间隔上采样。

基于FPGA的DSP开发技术正弦发生器模块设计实例第二步:利用Simulink进行模型仿真4)设置仿真参数。在SinOut模型窗口中,单击Simulation菜单,在下拉菜单中选择Simulationparameters,弹出SinOut模型的仿真参数设置对话框。

基于FPGA的DSP开发技术设置仿真时间,单位秒

基于FPGA的DSP开发技术正弦发生器模块设计实例第二步:利用Simulink进行模型仿真5)启动仿真,观察仿真结果。在SinOut模型窗口中,选中Simulation菜单下的Start项,开始仿真,仿真结束后,双击Scope模块,打开Scope观察窗,即可观察模型仿真结果。

基于FPGA的DSP开发技术完成第二步基于Simulink的模型仿真进行第三步——利用SignalCompiler实现算法到硬件转化

基于FPGA的DSP开发技术正弦发生器模块设计实例第三步:利用SignalCompiler实现算法到硬件转化1)模型分析,双击SinOut模型中的”SignalCompiler”图标。单击”Analyze”按钮,SignalCompiler将会对模型进行分析,检查模型有无错误。如果设计存在错误,将会停止分析过程,并在Matlab软件的命令窗口中给出相关信息。如果设计不存在错误,则在分析结束后打开”SignalCompiler”窗口。

基于FPGA的DSP开发技术正弦发生器模块设计实例第三步:利用SignalCompiler实现算法到硬件转化2)设置SignalCompiler工程设置部分文件转化、硬件编译部分信息报告部分

基于FPGA的DSP开发技术正弦发生器模块设计实例第三步:利用SignalCompiler实现算法到硬件转化2)设置SignalCompiler选择器件系列:不能指定具体器件型号选择综合器:Mentor的LeonardoSpectrum综合器Synplicity的Synplify综合器Altera的QuartusII优化选择:指定综合、适配过程的优化策略,面积、速度、平衡系统主时钟频率设置系统复位信号设置嵌入式逻辑分析仪设置仿真测试文件生成的选择生成DSP模块的SOPCBuilderPTF文件转换MDL到VHDL,生成一个VerilogHDL的模型和测试文件

基于FPGA的DSP开发技术正弦发生器模块设计实例第三步:利用SignalCompiler实现算法到硬件转化3)模型文件转换成HDL文件点击“ConvertMDLtoVHDL”的图标,执行mdl模型文件到VHDL文件的转换

基于FPGA的DSP开发技术正弦发生器模块设计实例第三步:利用SignalCompiler实现算法到硬件转化4)综合单击步骤2-synthesis的图标,执行综合过程。综合过程完成之后,信息框中会给出此项目的一些信息:如器件的系列,使用的逻辑宏单元的数目、触发器的数目、引脚数、RAM容量等

基于FPGA的DSP开发技术正弦发生器模块设计实例第三步:利用SignalCompiler实现算法到硬件转化5)适配单击步骤3-QuartusIIFitter的图标,调用QuartusII完成编译适配过程,生成编程文件:pof文件和sof文件转化、综合、适配三步也可点击该按钮一步执行

基于FPGA的DSP开发技术正弦发生器模块设计实例第三步:利用SignalCompiler实现算法到硬件转化6)编程完成转化、综合、适配三步后,“ProgramDevice”图标由不可用变为可用,即可以编程下载了。但程序下载之前,还要做一些必要的仿真:RTL级仿真、时序仿真等

基于FPGA的DSP开发技术完成第三步:利用SignalCompiler实现算法到硬件转化进行第四步——利用ModelSim进行RTL级仿真

基于FPGA的DSP开发技术正弦发生器模块设计实例第四步:利用ModelSim进行RTL级仿真Simulink中的模型仿真属于系统级(算法级)仿真,由Mdl文件转化而来的VHDL描述是RTL级的,转换后的代码实现可能与Mdl模型描述的情况不完全相符:需要针对生成的RTL级HDL代码进行RTL级仿真。在SignalCompiler设置窗口中的Testbench页中选中”GenerateStimuliforVHDLTestbench”,DSPBuilder在Mdl转换到VHDL的过程中会生成针对HDL仿真器ModelSim的测试文件。

基于FPGA的DSP开发技术正弦发生器模块设计实例第四步:利用ModelSim进行RTL级仿真仿真方法:启动ModelSim软件,选择Tools菜单下的ExecuteMacro…,在打开的文件选择对话框中切换到SinOut模型SinOut.mdl文件所在的目录,选择tb_SinOut.tcl,ModelSim执行tb_SinOut.tcl,开启仿真。

基于FPGA的DSP开发技术正弦发生器模块设计实例第四步:利用ModelSim进行RTL级仿真仿真结果显示:仿真结果默认是以数字形式显示的,为了与Simulink中的仿真结果相比,选中”tb_sinout/outu”,单击右键,在弹出菜单中选择properties…,在出现的waveproperties窗口中设置波形显示方式

基于FPGA的DSP开发技术正弦发生器模块设计实例第四步:利用ModelSim进行RTL级仿真Radix设为Unsigned选中AnalogHeight设为100Scale设为0.4

基于FPGA的DSP开发技术正弦发生器模块设计实例第四步:利用ModelSim进行RTL级仿真

基于FPGA的DSP开发技术完成第四步:利用ModelSim进行RTL级仿真进行第五步——利用QuartusII进行时序仿真

基于FPGA的DSP开发技术正弦发生器模块设计实例第五步:利用QuartusII进行时序仿真基于ModelSim的RTL级仿真是电路的功能仿真,其仿真结果未反映硬件时序的真实情况:需要进行时序仿真。SignalCompiler已经生成了利用QuartusII进行时序仿真的激励文件sinout.vec和相关仿真文件sinout_quartus.tcl,可以很容易地在quartusII中实现时序仿真。

基于FPGA的DSP开发技术正弦发生器模块设计实例第五步:利用QuartusII进行时序仿真仿真方法:1)启动quartusII集成开发环境,执行File菜单的OpenProject…的操作,选择Sinout模型所在的目录,打开DSPBuilder为QuartusII建立的设计项目——Sinout,并在项目中打开VHDL顶层设计文件sinout.vhd;2)指定器件的具体型号,编译顶层设计文件sinout.vhd;3)执行Processing菜单的StartSimulation命令,启动时序仿真。

基于FPGA的DSP开发技术正弦发生器模块设计实例第五步:利用QuartusII进行时序仿真

基于FPGA的DSP开发技术完成第五步:利用QuartusII进行时序仿真进行第六步——硬件实现与测试

基于FPGA的DSP开发技术正弦发生器模块设计实例第六步:硬件实现与测试1)根据硬件电路的具体接口方式,如DA芯片,修改生成的VHDL文件,添加相应的引脚,编译,仿真。2)FPGA芯片引脚的锁定,编译3)编程下载:利用QuartusII编程工具

基于FPGA的DSP开发技术完成第六步:硬件实现与测试至此,经过六步操作,已经利用DSPBuilder完整地实现了正弦发生器模块的设计。

基于FPGA的DSP开发技术MATLAB/DSPBuilder软件DSPBuilder简介基于DSPBuilder的DSP模块开发流程正弦发生器模块设计实例DSPBuilder层次性设计FIR数字滤波器设计实例层次性设计方法FDATool使用利用MegaCore的设计

基于FPGA的DSP开发技术DSPBuilder层次性设计DSPBuilder层次性设计主要用于搭建复杂的DSP系统,方便系统的设计与调试。DSPBuilder层次性设计的方法:利用DSPBuilder软件工具,将设计好的DSP模型生成子系统(Subsystem),将子系统与其他模块互联构成更大的系统。子系统可以被任意复制到其他模型文件中,双击子系统图标即可打开子系统源文件,子系统中还可以包含子系统。

基于FPGA的DSP开发技术MATLAB/DSPBuilder软件DSPBuilder简介基于DSPBuilder的DSP模块开发流程正弦发生器模块设计实例DSPBuilder层次性设计FIR数字滤波器设计实例层次性设计方法FDATool使用利用MegaCore的设计

基于FPGA的DSP开发技术FIR数字滤波器设计实例1)FIR滤波器原理FIR滤波器:FiniteImpulseResponse,有限冲激响应N-1阶FIR滤波器的系统函数为其差分方程表达式为3个延迟单元、4个乘法器、3个加法器(一个4输入加法器)

基于FPGA的DSP开发技术FIR数字滤波器设计实例2)采用层次性设计的16阶FIR滤波器设计2-1)设计一个h(0)为0的4阶滤波器考虑到浮点运算在FPGA实现的复杂性,采用定点运算,并省去小数定标,采用整数运算实现

基于FPGA的DSP开发技术FIR数字滤波器设计实例2)采用层次性设计的16阶FIR滤波器设计2-1)设计一个h(0)为0的4阶滤波器

基于FPGA的DSP开发技术FIR数字滤波器设计实例2)采用层次性设计的16阶FIR滤波器设计2-2)将设计的h(0)为0的4阶滤波器生成子系统

基于FPGA的DSP开发技术FIR数字滤波器设计实例2)采用层次性设计的16阶FIR滤波器设计2-3)利用4阶滤波器子系统搭建16阶FIR滤波器

基于FPGA的DSP开发技术FIR数字滤波器设计实例2)采用层次性设计的16阶FIR滤波器设计2-4)利用FDATool进行滤波器系数的设计启动FDATool:在MATLAB的命令窗口中输入fdatool回车即可启动,进入滤波器设计界面

基于FPGA的DSP开发技术参数设置完毕,点击滤波器设计按钮

基于FPGA的DSP开发技术

基于FPGA的DSP开发技术利用FDATool的滤波器性能分析

基于FPGA的DSP开发技术利用FDATool的滤波器性能分析

基于FPGA的DSP开发技术利用FDATool生成滤波器系数:Analysis-FilterCoefficients点击量化参数按钮

基于FPGA的DSP开发技术利用FDATool生成滤波器系数选择定点计算

基于FPGA的DSP开发技术利用FDATool生成滤波器系数

基于FPGA的DSP开发技术利用FDATool生成滤波器系数——量化误差分析设置输入、输出参数量化误差分析

基于FPGA的DSP开发技术利用FDATool生成滤波器系数——导出滤器系数,并转化成整数点击file菜单的export

基于FPGA的DSP开发技术FIR数字滤波器设计实例2)采用层次性设计的16阶FIR滤波器设计2-5)将利用FDATool设计的滤波器系数代入到设计的模型文件中,使用SignalCompiler将模型文件转换成VHDL文件,编译、下载,就完成了16阶FIR数字滤波器的设计

基于FPGA的DSP开发技术MATLAB/DSPBuilder软件DSPBuilder简介基于DSPBuilder的DSP模块开发流程正弦发生器模块设计实例DSPBuilder层次性设计FIR数字滤波器设计实例层次性设计方法FDATool使用利用MegaCore的设计

基于FPGA的DSP开发技术3)利用MegaCore实现16阶FIR滤波器设计3-1)添加FirCompiler:在Simulink的ALTERADSPBuilder库中选择MegacoreFunction子库,在其中选择fir_compiler模块

基于FPGA的DSP开发技术FIR数字滤波器设计实例3)利用MegaCore实现16阶FIR滤波器设计3-2)设置FirCompiler模块:双击fir_compiler模块点击该按钮,进行滤波器配置

基于FPGA的DSP开发技术FIR数字滤波器设计实例点击新建或编辑参数按钮

基于FPGA的DSP开发技术FIR数字滤波器设计实例可以导入FDATool设计的滤波器系数

基于FPGA的DSP开发技术FIR数字滤波器设计实例

基于FPGA的DSP开发技术FIR数字滤波器设计实例系数设计完成,回到主界面,进行滤波器设计相关配置

基于FPGA的DSP开发技术FIR数字滤波器设计实例3)利用MegaCore实现16阶FIR滤波器设计3-3)生成滤波器点击该按钮,生成滤波器

基于FPGA的DSP开发技术FIR数字滤波器设计实例3)利用MegaCore实现16阶FIR滤波器设计3-3)生成滤波器FIR模块成为一个参数化了的具体模块

基于FPGA的DSP开发技术FIR数字滤波器设计实例3)利用MegaCore实现16阶FIR滤波器设计基于Simulink的ALTERADSPBuilder,利用MegaCore进行FIR设计同样的,基于QuartusII,也可以利用MegaCore进行FIR设计更方便大型系统的仿真、设计

基于FPGA的DSP开发技术FIR数字滤波器设计实例IIR数字滤波器的设计快速傅里叶变换器设计基于基本模块的伪随机序列发生器设计基于MegaCore的伪随机序列发生器设计DSPBuilder常用的MegaCore

基于FPGA的DSP开发技术FIR数字滤波器设计实例总结与讨论:FIR数字滤波器的设计实现方法1)按照FIR原理的一般设计2)逻辑复用设计

基于FPGA的DSP开发技术MATLAB/DSPBuilder软件DSPBuilder简介基于DSPBuilder的DSP模块开发流程正弦发生器模块设计实例DSPBuilder层次性设计FIR数字滤波器设计实例层次性设计方法FDATool使用利用MegaCore的设计

1.说明DSPBuilder的主要功能。2.说明DSPBuilder的设计流程3.论述Matlab、Simulink、DSPBuilder、ModelSim、QuartusII几种软件工具之间的关系。作业

《伤寒学》讲义伤寒论教研室李赛美

第二章太阳病辨证论治

概论

一、太阳生理:抗御外邪入侵(人身屏障)调节汗液排泄管理水液代谢(膀胱州都之官)太阳之气又言表气(部位)卫气(功能)

太阳之气与下列脏腑相关:肾-肾阳温煦(肾与膀胱相表里)胃-胃中津气滋养肺-肺气宣发与敷布。足太阳膀胱经循行部位:起于目内目此,上头行项,夹脊,行人身之背。

二、太阳病理太阳病是表气受邪而致营卫失调的病变。病因:外感风寒病机:外邪袭表,正邪交争,营卫失调病位:表病性:表寒证

三、太阳病诊断与分型诊断主要依据是脉证,经络症状为辅。主证:头痛(项强)、恶寒主脉:脉浮腑证:小便不利经络症状:项背强直挛急

分类:太阳中风-表虚证,桂枝汤证太阳伤寒-表实证,麻黄汤证太阳温病

四、太阳病治则本证:中风表虚证-解肌祛风,调和营卫伤寒表实证-辛温发汗,宣肺平喘太阳温病-辛凉解表兼证-主治方加减变证-随证治之疑似证-注意鉴别

五、太阳病转归病愈-治疗得当,正复邪退传经-正退邪盛,病情发展伤阳寒化传三阴伤阴热化传阳明、少阳变证-治不如法,失治误治

第一节太阳病辨证纲要一.太阳病提纲(原文1/P21)太阳病病因:风寒袭表脉:浮-正气抗邪于外,气血充盈于表(定位)证头项强痛-经气郁遏不舒(定位)恶寒-风寒外束,表气被遏(定性)

释疑:1.为何未提发热?省文。发热是正气抗邪的反应,与脉浮机理一致。或未发热。恶寒与发热相比,恶寒更为重要,后人云“有一分恶寒,必有一分表证”恶寒起病即见,发热出现较迟。

2.二证一脉,最能揭示太阳病本质:风寒袭表,经气不利,正邪交争,营卫失调,最具诊断意义,故列为太阳病提纲证。3.必须是这组脉证同时出现。任何一个症状单独出现不一定是表证。

二、太阳病分类太阳中风证脉证提纲。(原文2/P22)太阳病中风证病因:风寒袭表证发热-气血外达,正邪相争汗出-卫外不固,营阴失守恶风-汗出肌疏,不胜风寒脉(浮)缓:肌腠被伤,经气外泄,营阴不足

释疑:“太阳病”有二种含义:太阳病脉证;病因概念-感受风寒之邪。为省文笔法。本条所列脉证,以汗出最重要。

病理性汗出,不能与使用发汗药引起的汗出相提并论。病理特点:感受风寒,卫气受伤,营阴失守临床特点:初起即见发热,但体温不高,怕冷不甚而恶风,汗自出。

太阳伤寒证主要脉证(原文3/P23)太阳伤寒证病因:寒邪袭表证发热体质较强者,恶寒与发热并见体质较弱者,先恶寒后发热必恶寒---不论发热与否,必先见恶寒-----卫阳被遏体痛---寒邪外束,经脉受阻,运行不畅呕逆---毛窍壅滞,卫气不通,胃气上逆脉:阴阳俱紧寒邪束表,肌腠收缩,寸尺两部脉来绷急

释疑:原文2.3.6条均不提“太阳之为病…..”,而提“太阳病名为……”第1条为提纲证,2.3.6条为太阳病分类。凡见脉紧必无汗,故汗不出当为太阳表实证的辨证要点。临床特点:发热较迟,体温较高,恶寒亦甚,皮肤干热。病理特点:风寒袭表,腠理致密,卫阳被遏,营阴郁滞

太阳温病的脉证提纲及误治后变证(原文6/P24)病证病因脉证特点治则后果中风伤寒风寒发热恶寒口不渴汗出脉浮缓无汗脉浮紧解肌祛风辛温发汗伤阳温病温热发热不恶寒口渴脉浮数辛凉解表伤阴

误治后变证:误汗(病位在心肺)身灼热-津伤热盛脉阴阳俱浮-热邪充斥于表,气血外应自汗出-热盛迫津外泄身重-热伤津气多眠睡-热扰心神鼻息必鼾-邪热上壅,肺窍不利语言难出-心神被扰(心主言,舌为苗窍)

误下(病位在肾)小便不利-热夺阴液,化源枯竭直视-热盛阴伤动风失溲-热扰神明(二便自遗)

误火(病位在肝)微发黄色----火热之邪加于温热,熏灼肝胆,胆汁外泄剧则如惊痫、时瘛疭,若火熏之------热动肝风,水不涵木。一逆尚引日:一次误治,尚有图治之机,再逆促命期:再次误治,促其寿命夭亡。

三、辨病发于阳与病发于阴辨外感病阴阳两大证型及愈期的判断(原文7/P26)病发于阳:发热恶寒-阳经受病,愈期-七日病发于阴:无热恶寒-阴经受病,愈期-六日

发热恶寒-正气能与邪气相争-亢奋状态太阳病-发热恶寒阳明病-但热不寒少阳病-往来寒热无热恶寒-正气无力与邪气相争-抑制状态太阴病-脾虚寒湿少阴病-心肾阳虚厥阴病-虚寒致厥发于阳(阳证)正盛邪实祛邪为主发于阴(阴证)阳虚阴盛扶正为先

释疑:关于“阳数七,阴数六”出于伏羲氏河图生成数顺序说:“七”为第一,“六”为第二,发于阳的先愈,发于阴的后愈季节说:七和六是指代春夏和秋冬

四、辨太阳病传变与否(原文4/P27)依据脉证,判断太阳病传与不传历代有不同说法认为颇欲吐是少阳主证、躁烦是阳明主证-病传少阳、阳明欲吐与躁烦看成阳明热证-邪传阳明欲吐不吐与躁动不安为少阴阴寒极盛-邪传少阴欲知是否传变,则需以脉证为依据

(原文5/P27)承上条,再论太阳病不传变伤寒有一日传变者伤寒亦有二三日不传者不拘于发病日数的多寡,以脉证为依据。

太阳病有自愈之机及预防传经之法(原文8/P28)“七日以上自愈者,以行其经尽故也”?与第7条“发于阳者,七日愈”说法一脉相承太阳病为阳病,当在阳数之期愈。在愈前的第6日,当太阳之期已过,邪气已衰,故为病愈。

文中仅举出头痛一证,临床当与发热恶寒项强脉浮等证合参太阳病病情若有向里发展之势,可先安未受邪之地。针足阳明经穴,疏通经气,振奋胃阳,扶正却邪,防止传经之变。

预测太阳病邪解后病愈日期(原文10/P29)太阳病余邪未清,或正气未复,不必再药只需休息调养,待正渐复,邪渐去,便可全愈十二日,为约略之词,不可拘泥

第二节太阳病本证一、中风表虚证(一)桂枝汤证原文12/P30分析:论述了桂枝汤证的主要症状与基本病机及《伤寒论》第一方桂枝汤。

太阳中风(包括1、2条脉证)脉阳浮-轻取浮阴弱-重按弱病机阳浮:热自发-卫强,抗邪于外而发热阴弱:汗自出-营弱,不能内守而汗出。主证嗇嗇恶寒-汗出窍开,遇寒则恶淅淅恶风-自汗营弱,遇风则恶翕翕发热-正气抗邪,体温不高辅证鼻鸣-肺气不利而鼻塞干呕-胃气不降治疗桂枝汤-调和营卫,解肌祛风

服法:①药后啜粥②温覆微汗③获效停服④未效守方⑤药后禁口

进一步讨论桂枝汤证的主证(原文13/P14)太阳病-泛指一切表证头痛、发热、恶风-表证共有证象汗出-为桂枝汤独具之证。

补述太阳中风的病因病机及证治(原文95/34)太阳病证-发热汗出病机营弱卫强病因-风邪偏盛治疗-桂枝汤-解肌祛风,调和营卫卫气浮盛于外营阴不能内守汗出

太阳中风证,邪气较重,当针药并用的治法(原文24/P34)反烦不解者-邪气较重,初服桂枝汤,正气得药力之助,正邪搏击治-针药并用。

太阳病脉象浮弱者,宜用桂枝汤(原文42/P34)太阳病证:外证未解-头痛发热恶风寒等证犹在脉浮弱浮缓-阳浮而阴弱浮弱-体弱不任峻汗治:当以汗解-解肌祛风方:宜桂枝汤

太阳病宜汗忌下的治疗原则(原文44/P34)表里同病先表后里表里同治,不可单用攻下法

太阳病汗下后,病仍在表,未成变证,仍当解表(原文45条/P34)太阳病误治先发汗不解-汗不如法而复下之-误用攻下目前情况:脉浮,病不愈原因:浮为在外,而反下之,故令不愈诊断:今脉浮,故在外-表证仍在治疗-当须解外-宜桂枝汤(轻汗)

太阳病误下后,其气上冲的治法(原文15/P34)太阳病误治-下转归其气上冲-正未伤,抗邪于外,表证仍在-桂枝汤若不上冲-正已伤,外邪内陷,变生他病-不可与桂枝汤

太阳伤寒发汗后,余邪未尽仍宜汗解的治法(原文57/34)病人原发病-太阳伤寒证治疗经过-发汗已解服麻黄汤伤寒脉证已愈目前表现-半日许复烦余邪未尽,移时复发汗出肌疏,复感风寒脉浮数-发热使然治疗-可更发汗-再次发汗,但改变其手段方-宜桂枝汤-轻汗

病常自汗出的病理和治疗(原文53/P37)病人证-常自汗出因-营气自和,卫气不谐-即营卫失调治-使营卫协调-宜桂枝汤

时发热自汗出的病理和证治(原文54/P37)病人证脏无他病----在内之脏腑无病时发热、自汗出而不愈----病系在外因:卫气不和----营卫不协调治:先其时发汗----在发热自汗出之前---服药方:宜桂枝汤

主症病理病证特点病机区别53条54条自汗营卫不和,关键在卫气常自汗出,无他症时发热自汗出卫气虚弱不能固外(开而不阖)卫虚,发散阳热功能降低阳郁肌表(阖而不开)

卫阳不足自汗症,服药有二种情况:无发热,但常自汗出者:表阳虚不能外固-----温复卫阳,其汗自止(不拘时)时发热,自汗出者卫阳虚郁,郁久生热,营阴受迫-----应在未发热之前服桂枝汤------温通卫阳,其汗自止。

桂枝汤的服法:用于卫阳不足的自汗,在于扶正,无须喝热粥以助汗用于太阳中风证,宜喝热粥助胃气,发汗祛邪

桂枝汤调营卫-调气血-调阴阳(适应证共13条)1.太阳中风证2.表证或汗或下,而外证未解,需再汗者3.太阳病,六七日不大便,小便清者4.杂病中,脏无他病,常自汗出,或时发热汗出者。5.霍乱病里和而表未解,身痛不休者'

您可能关注的文档

- 最新基因对性状的控制课件PPT课件.ppt

- 最新基因功能研究技术课件PPT.ppt

- 最新基因修饰在人源化肝脏小鼠建模中的应用课件PPT.ppt

- 最新基于阈值和区域生长法的图像分割方法课件PPT.ppt

- 最新基于素质模型的结构化面试三只眼(精简版)[PPT课件]课件PPT.ppt

- 最新基于热电偶温度传感器的动态温度实时测量记录系统设计.课件PPT.ppt

- 最新基于机器视觉技术发动机曲轴轴瓦分级检测系统应用研究课件PPT.ppt

- 最新基于听感知的 音频信息隐藏研究课件PPT.ppt

- 最新基于决策树改进CART算法的ANFIS结构辨识技术-(1)课件PPT.ppt

- 最新基于DSP的汽车运行状况监测系统硬件设计课件PPT.ppt

- 最新培达血管外科课件PPT.ppt

- 最新培训机构的家长沟通课件PPT.ppt

- 最新城轨交通信号系统-简介课件PPT.ppt

- 最新城市水务的融资详解课件PPT.ppt

- 最新城市大脑课件PPT.ppt

- 最新埃博拉出血热相关病例诊断和处理路径课件PPT.ppt

- 最新垫料湖北中医药大学中医药中心课件PPT.ppt

- 最新垃圾分类PPT-1课件PPT.ppt