- 838.00 KB

- 2022-04-29 14:26:47 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

'存储系统的基本概念(精)

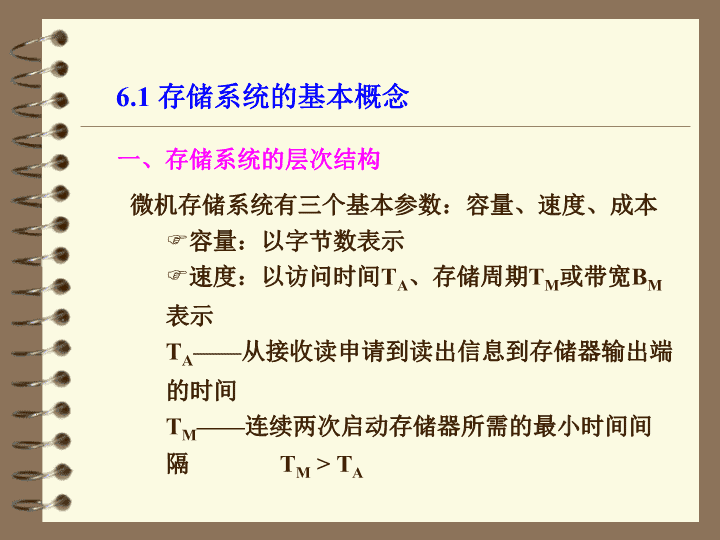

6.1存储系统的基本概念一、存储系统的层次结构微机存储系统有三个基本参数:容量、速度、成本容量:以字节数表示速度:以访问时间TA、存储周期TM或带宽BM表示TA——从接收读申请到读出信息到存储器输出端的时间TM——连续两次启动存储器所需的最小时间间隔TM>TA

一、存储系统的层次结构w——数据总线宽度成本:以每位价格表示存储系统的基本概念

二、存储器访问的局部性原理存储系统的基本概念存储器访问的局部性指处理器访问存储器时,无论取指令还是取数据,所访问的存储单元都趋向于聚集在一个较小的连续单元区域中。时间上的局部性——最近的将来要用到的信息很可能就是现在正在使用的信息。主要由循环造成空间上的局部性——最近的将来要用到的信息很可能与现在正在使用的信息在空间上是邻近的。主要由顺序执行和数据的聚集存放造成

二、存储器访问的局部性原理存储系统的基本概念存储器的层次结构是依靠存储器访问的局部性实现的存储器的层次结构的性能由命中率来衡量:命中率——对层次结构存储系统中的某一级存储器来说,要访问的数据正好在这一级的概率

二、存储器访问的局部性原理存储系统的基本概念例:两级存储系统M1访问时间TA1,命中率HM2访问时间TA2则平均访问时间TA=HTA1+(1-H)TA2规定:访问时间比访问效率则

二、存储器访问的局部性原理存储系统的基本概念追求101.01.0r=1r=2r=10r=100eH

6.2半导体存储器一、半导体存储器的分类RAM静态RAM(SRAM)动态RAM(DRAM)ROM掩膜型ROM可编程ROM(PROM)可擦除可编程ROM(EPROM)电可擦除可编程ROM(E2PROM)

半导体存储器二、半导体存储器的组成P.157三、静态RAM(SRAM)SRAM基本存储电路P.159

半导体存储器三、静态RAM(SRAM)存储矩阵地址译码器地址寄存器地址总线读写放大器数据寄存器数据总线控制电路OEWECESRAM芯片的结构

半导体存储器三、静态RAM(SRAM)SRAM的特点读写速度快所用管子数目多,单个器件容量小T1、T2总有一个处于到通状态,功耗较大SRAM通常用来做Cache

四、动态RAM(DRAM)半导体存储器行选择信号列选择信号数据输入输出线刷新放大器单管动态存储电路

四、动态RAM(DRAM)半导体存储器存储矩阵地址总线I/O缓冲器数据总线读写控制/动态刷新电路RAS#DRAM芯片的结构地址锁存器CAS#WE#

四、动态RAM(DRAM)半导体存储器DRAM的特点所用管子少,芯片位密度高功耗小需要刷新存取速度慢DRAM主要用来做内存

四、动态RAM(DRAM)半导体存储器DRAM的种类FPMDRAM存取时间80~100nsEDODRAM存取时间50~70nsSDRAM存取时间6~10ns

SIMM——SingleInlineMemoryModule单列直插式内存模块72线:32位数据、12位行列公用地址、RAS#、CAS#等在Pentium微型机中必须成对使用FPM/EDO四、动态RAM(DRAM)半导体存储器DRAM内存条的种类

DIMM——DualInlineMemoryModule双列直插式内存模块168线:64位数据、14位行列公用地址、RAS#、CAS#等可单数使用FPM/EDO/SDRAM四、动态RAM(DRAM)半导体存储器DRAM内存条的种类

五、只读存储器(ROM)P.166六、内存的扩展P.169位扩展地址扩展将多个内存芯片用位扩组装成内存模块(即内存条)将多个内存条插到内存插槽中——地址扩展半导体存储器

七、内存的奇偶校验处理器存储器阵列DRAM0DRAM1DRAM2DRAM3DRAM4DRAM5DRAM6DRAM7DRAMPB奇偶检查器/产生器PB8位9位PEPE半导体存储器

半导体存储器八、内存地址分析译码器74LS138

半导体存储器八、内存地址分析例:2764为8K8的EPROM芯片,要求其地址范围是FA000H~FBFFFH,设计其连线。

半导体存储器九、Pentium与内存的连接82439TX系统控制器(MTXC)

半导体存储器九、Pentium与内存的连接82439TX系统控制器(MTXC)

半导体存储器九、Pentium与内存的连接

6.3高速缓冲存储器(Cache)一、Cache的工作原理Cache的结构02n-1主存1块0块M-1M个块每块K个字节Cache标签块0C-1C个槽每个槽K个字节

高速缓冲存储器(Cache)一、Cache的工作原理地址映象直接映象每个主存块只允许放到Cache的特定的槽中优点:简单缺点:Cache命中率低、Cache空间利用率也低字节号槽号标签

高速缓冲存储器(Cache)一、Cache的工作原理地址映象全相联映象每个主存块允许放到Cache的任何一个槽中字节号标签优点:复杂优点:Cache命中率高、Cache空间利用率也高

高速缓冲存储器(Cache)一、Cache的工作原理地址映象组相联映象把Cache分成若干组,每组若干个槽。设每组有J个槽,称为J路组相联每个主存块允许放在特定组内的任意一个槽中字节号组号标签

高速缓冲存储器(Cache)一、Cache的工作原理替换算法1.最近最少使用(LRU)需要记录使用情况的历史信息2.先进先出(FIFO)用循环移位寄存器3.用得最少(LFU)每个槽增加一个计数器写入策略通写回写

高速缓冲存储器(Cache)二、Pentium的片内CacheCache分成独立的8K代码Cache和8K数据Cache采用二路组相联方式支持通写和回写两种写入方式采用LRU替换算法

高速缓冲存储器(Cache)二、Pentium的片内Cache

高速缓冲存储器(Cache)二、Pentium的片内Cache每个Cache有0路和1路两个4KB缓存组成Cache中数据操作的基本单元为32个字节,一个单元称为一个数据线,每个4KB缓存区有128个数据线片内Cache不能只填充部分数据线,这就是缓存式读总线周期要进行四个四字数据传送的原因每个4KB缓存区有一个与之对应的标记目录,每个标记目录含有128个标记表项,记录着数据线的使用情况以及数据线中的数据是否无效了

高速缓冲存储器(Cache)二、Pentium的片内Cache读操作命中未命中——进行高速缓存数据线填充读操作,在突发式读总线周期中读入256位数据写操作回写通写WB/WT#信号

高速缓冲存储器(Cache)二、Pentium的片内CacheCache的清除——两种方法:通过使FLUSH#输入低电平通过指令INVD、WBINVD

高速缓冲存储器(Cache)三、Pentium的外部Cache外部Cache称为二级Cache——L2Cache

高速缓冲存储器(Cache)三、Pentium的外部Cache

6.4微机的外部存储器磁表面存储器光盘存储器

神经-肌肉接点一、神经-肌肉接点兴奋的传递二、兴奋-收缩耦联三、肌肉收缩的形式

一、神经-肌肉接点兴奋的传递(一)运动单位1、概念2、运动单位活动原则

(二)兴奋在神经-肌肉接点的传递1、接点结构运动神经末梢轴突末梢膜囊泡含乙酰胆碱(Ach)接点间隙终板膜皱褶。

轴突末梢膜Ca2+通道开放,细胞外液中的Ca2+进入轴突末梢,触发囊泡移动以至排放。当ACh分子通过接点间隙到达终板膜表面时,与受体结合,出现的是Na+的内流和K+的外流,其总的结果是使终板膜去极化。2、兴奋传递

二、兴奋-收缩耦联(一)肌肉收缩的分子机制横小管将兴奋从肌膜传递到肌浆网后,肌浆网钙通道开放,大量Ca2+涌入肌浆,与细肌丝上的肌钙蛋白结合,暴露出肌动蛋白上的结合位点,横桥与其结合,靠ATP释放的能量,横桥拖动细肌丝向M线滑动。

横桥拖动细肌丝

Ach胆硷酯酶乙酸+胆碱许多药物可以作用于接点传递过程中的不同阶段,影响正常的接头功能。如,美洲箭毒和-银环蛇毒可以同ACh竞争终板膜的ACh受体亚单位,因而可以阻断接点传递而使肌肉失去收缩能力;有类似作用的药物称为肌肉松弛剂;有机磷农药等对胆碱酯酶有选择性的抑制作用,可造成ACh在接点和其他部位大量聚积,引起中毒症状。(二)Ach的清除

神经冲动停止,钙离子泵入终池,肌钙蛋白复原,原肌球蛋白掩盖结合位点,横桥与肌动蛋白分离,粗、细肌丝恢复原状。4.肌肉的舒张

(一)肌肉收缩形式三、肌肉收缩

1、缩短收缩1)等张收缩所加负荷不变,产生的张力随关节角度改变而改变。所谓等张收缩,实际上是指负荷在关节某一角度时的张力。2)等动收缩等动练习器能将负荷随关节运动的进程而精确调整。2、拉长收缩肌肉所产生的张力小于负荷。3、等长收缩张力=负荷。

1、单收缩——整块骨骼肌或单个肌细胞受到一次短促的刺激时,先是产生一次动作电位,紧接着出现一次机械收缩,后者称为单收缩。(二)肌肉收缩的外部表现

2、强直收缩

(三)骨骼肌不同收缩形式的比较1、离心收缩张力最大2、离心收缩代谢较低3、离心收缩肌肉容易酸痛

下次课讨论:离心收缩与运动健身'

您可能关注的文档

- 最新如何进行床边护理系统评估课件PPT.ppt

- 最新妇人妊娠病脉证并治第二十课件PPT.ppt

- 最新妈妈我要去旅行课件PPT.ppt

- 最新威尼斯小艇解析课件PPT.ppt

- 最新婴幼儿泌尿系统结石.课件PPT.ppt

- 最新婴幼儿大动作发展课件PPT.ppt

- 最新婴幼儿保健知识分析课件PPT.ppt

- 最新婴幼儿乳房发育概述课件PPT.ppt

- 最新孔型设计6资料课件PPT.ppt

- 最新孟子见梁惠王模板课件PPT.ppt

- 最新学习指导-7-非正弦周期电路课件PPT.ppt

- 最新学习情境2-半导体三极管及其放大电路.课件PPT.ppt

- 最新学习障碍类型课件PPT.ppt

- 最新学习能力与学习障碍课件PPT.ppt

- 最新学会倾听课件(心理健康教育课件)课件PPT.ppt

- 最新学会看病课件课件PPT.ppt

- 最新学前儿童生活保健制度课件PPT.ppt

- 最新学前儿童的亲子交往课件PPT.ppt