- 1.10 MB

- 2022-04-29 14:47:45 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

'基本数字逻辑单元的设计(1)

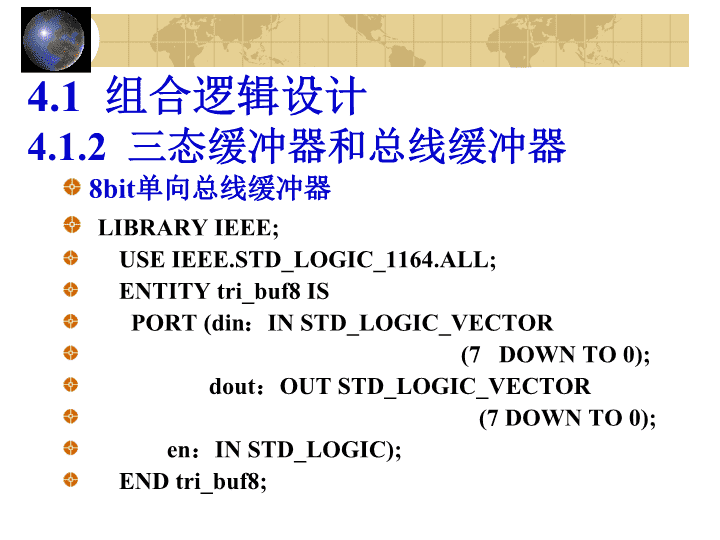

4.1组合逻辑设计4.1.2三态缓冲器和总线缓冲器8bit单向总线缓冲器LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYtri_buf8ISPORT(din:INSTD_LOGIC_VECTOR(7DOWNTO0);dout:OUTSTD_LOGIC_VECTOR(7DOWNTO0);en:INSTD_LOGIC);ENDtri_buf8;

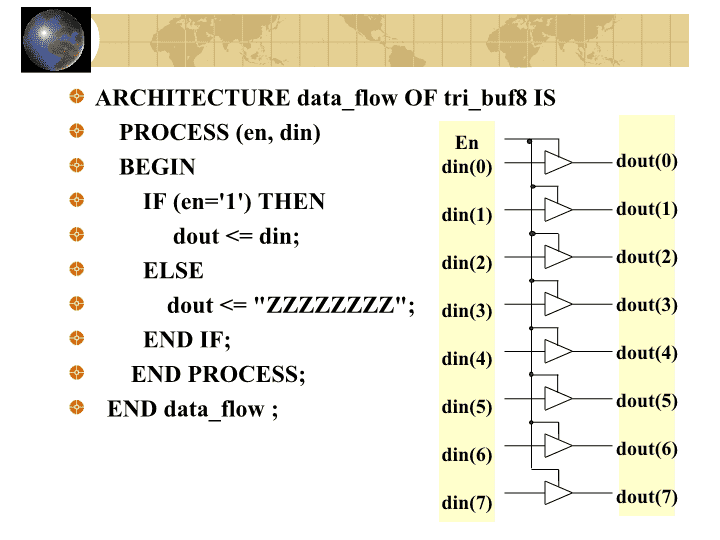

ARCHITECTUREdata_flowOFtri_buf8ISPROCESS(en,din)BEGINIF(en="1")THENdout<=din;ELSEdout<="ZZZZZZZZ";ENDIF;ENDPROCESS;ENDdata_flow;Endin(0)din(1)din(2)din(3)din(4)din(5)din(6)din(7)dout(0)dout(1)dout(2)dout(3)dout(4)dout(5)dout(6)dout(7)

BCD码—段选码译码器。BCD码输入与LED显示器字段的对应关系BCD码数字显示段hgfedcba0000011000000000111111100100102101001000011310110000010041001100101015100100100110610000010011171010011110008100000001001910010000其它11111111BCD-段选码译码器d0d1d2d3abc.hgdefVcc

LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYseg_delISPORT(d:INSTD_LOGICVECTOR(3DOWNTO0);q:OUTBIT_VECTOR(7DOWNTO0));ENDseg_del;ARCHITECTUREseg_rtlOFseg_delISBEGINPROCESS(d)BEGINCASEdISWHEN"0000"=>q<="11000000";WHEN"0001"=>q<="11111001";

WHEN"0010"=>q<="10100100";WHEN"0011"=>q<="10110000";WHEN"0100"=>q<="10011001";WHEN"0101"=>q<="10010010";WHEN"0110"=>q<="10000010";WHEN"0111"=>q<="11011000";WHEN"1000"=>q<="10000000";WHEN"1001"=>q<="10010000";WHENOTHERS=>q<="11111111";ENDCASE;ENDPROCESS;ENDseg-rtl;

4.1.4运算器的设计一位全加器的设计.LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYfull_adderISPORT(a,b,ci:INSTD_LOGIC;sum,cout:OUTSTD_LOGIC);ENDfull_adder;ARCHITECTURErtlOFfull_adderISBEGINsum<=aXORbXORci;cout<=(aANDb)OR(aANDci)OR(bANDci);ENDrtl;asumbcicout

4位串行进位加法器ciabsumcociabsumcociabsumcociabsumcoS0S1S2S3COCIA0B0A1B1A2B2A3B3SUMCIABSUMCIABSUMCIABSUMCIABCI0A0B0CI1A1B1CI2A2B2CIn-1An-1Bn-1进位产生逻辑S0S1S3Sn-1coutCIA[0:n-1]B[0:n-1]N位超前进位加法器

超前进位加法器各位加法器产生进位的逻辑表达式为:定义为进位生成函数,定义为进位传递函数,则全加器的各位和为:

4位超前进位加法器LIBRARYIEEE;USEIEEESTD_LOGIC_1164.ALL;ENTITYadder4ISPORT(a,b:INSTD_LOGIC_VECTOR(3DOWNTO0)ci:INSTD_LOGIC;sum:OUTSTD_LOGIC_VECTOR(3DOWNTO0);cout:OUTSTD_LOGIC);ENDadde4r;ARCHITECTURErtl_adder4OFadder4ISSIGNALg,p,c:STD_LOGIC_VECTOR(3DOWNTO0);BEGINp(0)<=a(0)ORb(0);p(1)<=a(1)ORb(1);p(2)<=a(2)ORb(2);g(0)<=a(0)ANDb(0);a[3:0]b[3:0]ciSum[3:0]cout

g(1)<=a(1)ANDb(1);g(2)<=a(2)ANDb(2);g(3)<=a(3)ANDb(3);c(0)<=g(0)OR(p(0)ANDci);c(1)<=g(1)OR(p(1)ANDg(0))OR(p(1)ANDp(0)ANDci);c(2)<=g(2)OR(p(2)ANDg(1))OR(p(2)ANDp(1)ANDg(0))OR(p(2)ANDp(1)ANDp(0)ANDci);c(3)<=g(3)OR(p(3)ANDg(2))OR(p(3)ANDp(2)ANDg(1))OR(p(3)ANDp(2)ANDp(1)ANDg(0))OR(p(3)ANDp(2)ANDp(1)ANDp(0)ANDci);cout=c(3);sum(0)<=a(0)XORb(0)XORci;sum(1)<=a(1)XORb(1)XORc(0);sum(2)<=a(2)XORb(2)XORc(1);sum(3)<=a(3)XORb(3)XORc(2);ENDrtl_adder4;

2.移位器8bit移位器。D7D6D5D4D3D2D1D0d7d6d5d4d3d2d1d0右移d0左移d7d6d5d4d3d2d1d0d7d6d5d4d3d2d1d0d7Irsrsldataa_outdata_inil

8bit移位器的VHDL程序。LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYshifterISPROT(data_in:INSTD_LOGIC_VECTOR(7DOWNTO0);sr,sl,ir,il:INSTD_LOGIC;data_out:OUTSTD_LOGIC_VECTOR(7DOWNTO0);ENDshifter;ARCHITECTUREAlgOFshifterISBEGINPROCESS(sr,sl,data_in,ir,il)VARIABLEcon:STD_LOGIC_VECTOR(0TO1);

BEGINcon:=sr&sl;CASEconISWHEN"00"=>data_out<=data_in;WHEN"01"=>data_out<=data_in(6DOWNTO0)&il;--左移WHEN“10”=>data_out<=ir&data_in(7DOWNTO1);--右移WHEN"11"=>data_out<=data_in;ENDCASE;ENDPROCESS;ENDAlg;

3.求补器LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;USEIEEE.STD_LOGIC_ARITH.ALL;USEIEEE.STD_LOGIC_UNSIGNED.ALL;ENTITYcomplementISPORT(a:INSTD_LOGIC_VECTOR(7DOWNTO0);b:UTSTD_LOGIC_VECTOR(7DOWNTO0));ENDcomplement;ARCHITECTURErtlOFcomplementISBEGINb<=NOTa+”00000001”;ENDrtl;

4.乘法器。部分积右移8bit乘法器的设计。LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;USEIEEE.STD_LOGIC_ARITH.ALL;USEIEEE.STD_LOGIC_UNSIGNED.ALL;ENTITYmultISPORT(ai,bi:INSTD_LOGIC_VECTOR(7DOWNTO0);Product:OUTSTD_LOGIC_VECTOR(15DOWNTO0);done:OUTSTD_LOGIC);ENDmult;

ARCHITECTUREshift_multOFmultISBEGINPROCESS(ai,bi)VARIABLEa,b,m:STD_LOGIC_VECTOR(8DOWNTO0);VARIABLEcount:INTEGER;BEGINa:="0"&ai;b:="0"&bi;count:=0;m:="00000000";done<="0";

WHILEcount<8LOOPIFa(0)="1"THENm:=m+bi;ENDIF;a:=m(0)&a(7DOWNTO1);m:="0"&m(7DOWNTO1);count:=count+1;ENDLOOP;product<=m(7DOWNTO0)&a(8DOWNTO1);done<="1";ENDPROCESS;ENDshift_mult;

4.1.5算术逻辑运算单元本例是一个8bit的ALU,能够完成8种运算,即加(add),带进位加(addc),减sub,带借位减法(subc),逻辑非、与、或和逻辑异或。alucoder程序包定义指令码。LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;PACKAGEalucoderISCONSTANTadd:STD_LOGIC_VECTOR(2DOWNTO0):="000";CONSTANTaddc:STD_LOGIC_VECTOR(2DOWNTO0):="001";CONSTANTsub:STD_LOGIC_VECTOR(2DOWNTO0):="010";

CONSTANTsubc:STD_LOGIC_VECTOR(2DOWNTO0):="011";CONSTANTnot:STD_LOGIC_VECTOR(2DOWNTO0):="100";CONSTANTand:STD_LOGIC_VECTOR(2DOWNTO0):="101";CONSTANTor:STD_LOGIC_VECTOR(2DOWNTO0):="110";CONSTANTxor:STD_LOGIC_VECTOR(2DOWNTO0):="111"ENDalucoder;

ALU运算模块设计。LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;USEIEEE_NUMERIC_STD.ALL;USEIEEE.STD_LOGIC_ARITH.ALL;USEIEEE.STD_LOGIC_UNSICNED.ALL;USEWORK.alucoder.ALL;ALUsalu_comandcyAcccoutover

ENTITYaluISPORT(s:INSTD_LOGIC_VECTOR(7DOWNTO0);cy:INSTD_LOGIC;alu_comand:INSTD_LOGIC_VECTOR(2DOWNTO0);Acc:INOUTSTD_LOGIC_VECTOR(7DOWNTO0);cout,over:BUFFERSTD_LOGIC);ENDalu;ARCHITECTUREalgOFaluISSIGNALr1,s1,f1:STD_LOGIC_VECTOR(8DOWNTO0);BEGINr1<="0"&Acc;s1<="0"&s;PROCESS(r1,s1,cy,alu_comand)BEGINCASEalu_comandIS

WHENadd=>f1<=r1+s1;WHENaddc=>IFcy="0"THENf1<=r1+s1;ELSEf1<=r1+s1+1;ENDIF;WHENsub=>f1<=r1+NOT(s1)+1;WHENsubc=>IFcy="0"THENf1<=r1+NOT(s1)+1;ELSEf1<=r1+NOT(s1);ENDIF;WHENnot=>f1<=NOT(r1);WHENand=>f1<=r1ANDs1;WHENor=>f1<=r1ORs1;WHENXOR=>f1<=r1XORs1;WHENOTHERS=>f1<="-";

ENDCASE;ENDPROCESS;Acc<=f1(7DOWNTO0);cout<=f1(8);over<=f1(8)XORf1(7);ENDalu;

4.2时序逻辑电路设计4.2.1触发器1.D触发器LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYdffISPORT(d,clk:INSTD_LOGIC;q:OUTSTD_LOGIC);ENDdff;ARCHITECTURErtl_ifOFdffISBEGINPROCESS(clk)BEGIN

IF(clk"EVENT"ANDclk=1)THENq<=d;ENDIF;ENDPROCESS;ENDrtl_if;结构体的另一种描述如下:ARCHITECTURErtl_waitOFdffISBEGINPROCESSBEGINWAITUNTILclk"EVENTANDclk=1;q<=d;ENDPROCESS;ENDrtl_wait;

4.2.3寄存器D0~D7:8位并行数据输入端。SI:串行数据输入端。Q7:串行数据输出端。Q0~Q6:内部寄存器数据输出端。clk:时钟。ckin:时钟信号禁止,只有当其无效时,移位寄存器才在时钟的触发下进行移位操作。S/L:移位(shift)/装入(load)。当此端为高电平时,可执行移位操作,当此端为低电平时,读入D0~D7端的并行数据。CLR:异步清零。D[7:0]SIS/LQ7clkckinclr

串/并入、串出移位寄存器LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYshifterISPORT(clr,si,ckin,clk:INSTD_LOGIC;d:INSTD_LOGIC_VECTOR(7DOWNTO0);q:OUTSTD_LOGIC);sl:INBIT);ENDshifter;ATCHITECTURErtl_shifterOFshifterISSIGNALtemp8:STD_LOGIC_VECTOR(7DOWNTO0);BEGIN

PROCESS(clr,sl,ckin,clk)IF(clr="0")THENtemp8<="00000000";q<=temp8(7);ELSIF(clk"EVENT)AND(clk="1")AND(ckin="0")THENIF(sl="0")THENtemp8<=d;--装入数据q<=d(7);ELSEq<=temp8(7);temp8(7)<=temp8(6);temp8(6)<=temp8(5);

temp8(5)<=temp8(4);temp8(4)<=temp8(3);temp8(3)<=temp8(2);temp8(2)<=temp8(1);temp8(1)<=temp8(0);temp8(0)<=si;ENDIF;ENDIF;ENDPROCESS;ENDrtl_shifter;

4.2.4计数器8位异步计数器的设计Q/QDclkQ/QDclkQ/QDclkQ/QDclkdclkclrcount_in(0)count_in(1)count_in(8)Q0Q1Q2Q7

计数器的顶层设计LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYriplecountISPORT(clk,clr:INSTD_LOGIC;count:OUTSTD_LOGIC_VECTOR(7DOWNTO0));ENDriplecount;ARCHITECTURErtl_riplecountOFriplecountISSIGNALcount_in:STD_LOGIC_VECTOR(8DOWNTO0);

COMPONENTdfftPORT(clk,clr,d:INSTD_LOGIC;Q:OUTSTD_LOGIC;Qn:BUFFERSTD_LOGIC);ENDCOMPONENT;--调用当前库中的同名实体作为元件BEGINcount_in(0)<=clk;genl:FOR:IN0TO7GENERATEU:dfftPORTMAP(clk=>count_in(i),clr=>clr;d=>count_in(i+1),,Q=>count(i);Qn=>count_in(i+1));ENDGENERATE;ENDrt_riplecountl;

--单个触发器性能描述LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYdfftISPORT(clk,clr,d:INSTD_LOGIC;Q:OUTSTD_LOGIC;Qn:BUFFERSTD_LOGIC);ENDdfft;ARCHITECTURErtldOFdfftISBEGIN

PROCESS(clk,clr)BEGINIF(clr="0")THENQ<="0";Qn<="1";ELSIF(clk"EVENTANDclk="1")THENQ<=d;Qn<=NOTd;ENDIF;ENDPROCESS;ENDrtld;

4.3存储器4.3.1概述存储器单元实际上是时序逻辑电路的一种。按存储器的使用类型可分为只读存储器(ROM)和随机存取存储器(RAM),两者的功能有较大的区别,因此在描述上也有所不同。存储器是许多存储单元的集合,按单元号顺序排列。每个单元由若干二进制位构成,以表示存储单元中存放的数值。这种结构和数组的结构非常相似,故在VHDL语言中,通常由数组描述存储器。

TYPEmemoryISARRAY(INTEGERRANGE<>)OFINTEGER;TYPEwordISSTD_LOGIC_VECTOR(k-1DOWNTO0);TYPEmemoryISARRAY(0TOw-1)OFword;

4.3.3随机存储器RAMLIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;USEIEEE.STD_LOGIC_ARITH.ALL;ENTITYram4kISGENERIC(k:INTEGER:=8;w:INTEGER:=12;rd_del,wr_del:TIME);PORT(WR,RD,CS:INSTD_LOGIC;Adr:INSTD_LOGIC_VECTOR(w-1DOWNTO0);D:INOUTSTD_LOGIC_VECTOR(k-1DOWNTO0));ENDram4k;WRRDCSAdr[11:0]Dout[7:0]

ARCHITECTUREbehavram4kOFram4kISTYPEmemoryISARRAY(0TO2**w-1)OFSTD_LOGIC_VECTOR(k-1DOWNTO0);SIGNALsram:memory;SIGNALAdr_in:INTEGER;BEGINAdr_in<=CONV_INEGER(Adr);--位矢量转换成整数PROCESS(WR,RD,CS)BEGIN

IFCS="0"THENIFRD="0"THEND<=sram(Adr_in)AFTERrd_del;ELSIFWR="0"THENsram(Adr_in)<=DAFTERwr_del;ENDIF;ELSED<=(OTHERS’Z’)AFTERrd_del;ENDIF;ENDPROCESS;ENDbehav;

4.3.2只读存储器ROM在用VHDL语言描述ROM时,ROM的内容应在仿真时先读到ROM中,这就是ROM的初始化。存储器的初始化要依赖于外部文件的读取,即由TEXTIO对ROM进行初始化。下面是对ROM进行初始化的实例。VARIABLEstartup:BOOLEAN:=TRUE;VARIABLEl:LINE;--LINE是在TEXTIO程序包定义的存取类型VARIABLEj:INTEGER;VARIABLErom:memory;FILEromin:TEXTISIN"rom2k.in";--TEXT是在TEXTIO程序包定义的文件类型

初始化程序:IFstartupTHENFORjINrom‘RANGELOOP--利用数据区间属性函数获得数组的上下限READLINE(romin,l);--从文件romin中读入一行放入l中。READ(l,rom(j));--从l中读入一个数据放入rom中ENDLOOP;ENDIF;G1G2Adr[11;0]Dout[7:0]

只读存储器ROM的VHDL程序。LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;USEIEEE.STD_LOGIC_ARITH.ALL;USESTD.TEXTIO.ALL;ENTITYrom4kISPORT(G1,G2:INSTD_LOGIC;Adr:INSTD_LOGIC_VECTOR(11DOWNTO0);dout:OUTSTD_LOGIC_VECTOR(7DOENTO0);ENDrom4k;

ARCHITECTUREbehav_rom4kOFrom4kISTYPEwordISSTD_LOGIC_VECTOR(7DOWNTO0);TYPEmemoryISARRAY(0TO4095)OFword;SIGNALadr_in:INTEGERRANGE0TO4095;VARIBLErom:memory;VARIBLEstartup:BOOLEAN:=TURE;VARIBLEl:LINE;VARIBLEj:INTEGER;FILEromin:TEXTISIN“rom2k.in”;--文件类说明.BEGINPROCESS(G1,G2)BEGIN

IFstartupTHENFORjINrom"RANGELOOPREADLINE(romin,l);READ(l,rom(j));ENDLOOP;startup:=FALSE;ENDIF;adr_in<=CONV_INTEGER(Adr);--将位矢量转换成整数.IF(G1="1"ANDG2="1")THENdout<=rom(adr_in);ELSEdout<="ZZZZZZZZ”;ENDIF;ENDPROCESS;ENDbehav_rom2k;

4.3.4先进后出堆栈先进后出堆栈是处理程序中断的常用数据结构,其数据存放结构和RAM是一致的,但存储方式有所不同。先进后出堆栈由2个功能块组成,即存储器体和堆栈指针SP,进堆时SP+1→SP指向下一个存储单元;出堆时SP-1→SP,并把SP所指示的存储单元的内容输出。din[7:0]pushpopclkresetDout[7:0]

256字节先进后出堆栈的VHDL程序。LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;USEIEEE.STD_LOGIC_ARITH.ALL;USEIEEE.STD_LOGIC_UNSIGNED.ALL;ENTITYstackISGENERIC(w:INTEGER:=256;k:INTEGER:=8);PORT(clk,reset,push,pop:INSTD_LOGICdin:INSTD_LOGIC_VECTOR(k-1DOWNTO0);dout:OUTSTD_LOGIC_VECTOR(k-1DOWNTO0));ENDstack;

ARCHITECTUREbehav_stackOFstackISTYPEmemoryISARRAY(0TOw-1)OFSTD_LOGIC_VECTOR(k-1DOWNTO0);SIGNALram:MEMORY;SIRNALsp:INTEGERRANGE0TOw-1;BEGINdout<=ram(sp);P1:PROCESS(clk)BEGINIF(clk"EVENTANDclk="1")THENIF(push="0")THENram(sp)<=din;ENDIF;ENDIF;ENDPROCESSP1;数据堆栈写

P2:PROCESS(clk,reset)BEGINIF(reset="1")THENsp<=0;ELSIF(clk"EVENTANDclk="0"ANDpush=’0’)THENsp<=sp+1;--在clk的后沿sp+1ElSIF(clk"EVENTANDclk="1"ANDpop=’0’)THENsp<=sp-1;--sp指针修改ENDIF;ENDPROCESSP2;ENDbehav_stack;加减计数器操作

4.4有限状态机有限状态机是时序电路的通用模型,任何时序电路都可以表示为有限状态机。对于大部分数字电子系统,都可以划分为控制单元和数据单元两个组成部分,控制单元的主体是一个有限状态机,它接收外部信号和数据单元产生的状态的信息,产生各种控制信号,决定何时进行何种数据处理。有限状态机分为两类:Moore型和Mealy型。次态逻辑状态寄存器输出逻辑输入次态现态输出

状态机的设计步骤定义状态机的各状态。适当地确定状态机的工作状态,是状态机设计的基础,需要充分利用设计者的设计经验。建立状态转换图。构造状态转换图时,通常从一个比较容易的状态开始。例如系统的初始状态、复位状态或空闲状态等,都是很好的起始状态。为每个状态标出转换的条件,相应的输入、输出信号。建立状态机进程。在VHDL程序中,通常用进程描述有限状态机。由于次态是现态及输入信号的函数,因此,往往将现态和输入信号作为进程的敏感信号。进程中定义状态的转移。所有的状态均可表达为CASE_WHEN结构中的一条CASE语句,利用CASEWHEN语句IF_THEN_ELSE语句实现状态的转移。

存储器控制器的设计存储器控制器的输入信号是微处理器的就绪ready和读写信号read_write。当上电复位或者ready有效时,存储器控制器开始工作,并在下一个时钟周期判断本次作业任务是读存储器还是写存储器,当read_write=‘1’时为读操作,使OE和CS信号有效,read_write=‘0’时为写操作,WE和CS信号有效。当ready信号再次有效时,结束本次读写操作,并使控制器返回到初始状态。存储器控制器readyread-writeOEWECS

存储器控制器状态转移图状态图decisionidlewritereadreadyreadyreadyreadyreadyreadyread_writeread_write

带异步复位的双进程状态机的存储器控制器设计。LIBRARYIEEEUSEIEEE.STD_LOGIC_1164.ALL;ENTITYmemoy_controllerISPORT(reset,read_write,ready,clk:INSTD_LOGIC;OE,WE,CS:OUTSTD_LOGIC);ENDmemory_controller;ARCHITECTUREstate_machineOFmemory_controllerISTYPEstatetypeIS(idle,decision,read,write);SIGNALpresent_state,next_state:STATETYPE;

带异步复位的双进程状态机的存储器控制器设计。state_comb:PROCESS(reset,present_state,read_write,ready)BEGINIF(reset="1")THENnext_state<=idle;OE<="0";WE<="0";CS<=‘0’;ELSECASEpresent_stateIS

WHENidle=>OE<="0";WE<="0";CS<="0";IFready="1"THENnext_state<=decision;ELSEnext_state<=idle;ENDIF;WHENdecision=>OE<="0";WE<="0";CS<="0";IF(read_write="1")THENnext_state<=read;ELSEnext_state<=write;ENDIF;

WHENread=>OE<="1";WE<="0";CS<=‘1";IF(ready="1")THENnext_state<=idle;ELSEnext_state<=read;ENDIF;WHENwrite=>OE<="0";WE<="1";CS<=‘1";IF(ready="1")THENnext_state<=idle;ELSEnext_state<=write;ENDIF;

WHENOTHERS=>OE<=‘0’;WE<=‘0’;CS<=‘0’;next_state<=idle;ENDCASE;ENDIF;ENDPROCESSstate_comb;

state_clocked:PROCESSBEGINWAITUNTILclk"EVENTANDclk="1";present_state<=next_state;ENDPROCESSstate_clocked;ENDstate_machine;PROCESS(1)CASE-WHENIF-THEN-ELSEPROCESS(2)WAITUNTILclk‘EVENTANDclk=‘1’输入次态现态

Whichsentencepatternisit?Shewasanauthorandshewrotethisgreatbook.Shewasanauthor.Shewrotethisgreatbook.Shewastheauthorwhowrotethisgreatbook.

Sentencepattern英语句式可分为三类:简单句(Simplesentence),并列句(Compoundsentence)复合句(Complexsentence)

当一个句子只包含一个主谓结构时称为简单句。含有两个或两个以上独立分句的句子叫并列句,这些独立分句处于平等的、互不依从的并列地位。复合句是一个主句和一个或一个以上的从句构成。主句是全句的主体,通常可以独立存在;从句则是一个句子成分,不能独立存在。但是从句也有主语和谓语部分。所不同在于,从句须由一个关联词引导,起到联系从句和主句的作用。

1.HarryPorterisaboy2.Hehasmagicpower.1.Idon"tlikelazypeople.我不喜欢不做家务的人。.

HarryPorterisaboywhohasmagicpower.先行词关系词定语从句关系代词关系副词which,who,whom,whose,that,aswhere,when,why被定语从句修饰的对象称为先行词重复指代先行词,起连接主句和从句的作用,并在从句中充当一定成分的连接词称为关系词。

1.Thewomanisafamousedancer.Shelivesnextdoor.2.Iknowafriend.Hisbrotherbrotherisapopsinger.3.Themanismyfriend.Youmetthemanonthestreetyesterday.4.Wearestudyingthisnovel.Itcontainsalotofinterestingstories.5.Tomwaslate.Thatsurprisedme.6.I"llneverforgettheday.Ontheday,Imetyou.7.Thisisthetown.Inthetown,Ispentmychildhood.8.Thisisthereason.Ididn"tcomeforthereason.

主语宾语定语指人指物(一)引导定语从句的关系代词who/thatwhichthatwhomwhothatwhichthatwhosewhose

关系副词先行词在从句中的成分时间时间状语地点地点状语reason原因状语(二)引导定语从句的关系副词whenwherewhy70'

您可能关注的文档

- 最新基础心理学串讲改课件PPT.ppt

- 最新基础心思学4 记忆课件PPT.ppt

- 最新多媒体数据压缩编码技术课件PPT.ppt

- 最新基础医学北大病理学PPT课件恶性上皮性肿瘤课件PPT.ppt

- 最新基础化学-第08章 氧化还原反应与电极电势课件PPT.ppt

- 最新基础会计课件PPT课件.ppt

- 最新基础会计课件-ch1-总论课件PPT.ppt

- 最新基础会计学课件(第一章)课件PPT.ppt

- 最新基础会计学(教学课件7)课件PPT.ppt

- 最新基本不等式说课课件完善课件PPT.ppt

- 最新基本不等式课件(最新)课件PPT.ppt

- 最新基层党建工作创新的思考课件PPT.ppt

- 最新基因身份证分析课件PPT.ppt

- 最新基因诊断技术的应用课件PPT.ppt

- 最新基因表达调控ppt课件课件PPT.ppt

- 最新基因组学技巧在致病基因发觉课件PPT.ppt

- 最新基因工程菌的发酵课件PPT.ppt

- 最新基因工程第2章 酶学基础(2dna连接酶)课件PPT.ppt